ポイント

- 次世代3次元半導体実装技術「BBCubeTM」を推進する、量産工程・接着材・電源供給技術の三つを開発

- コンデンサ・演算チップの高速高精度実装、ならびに電源ノイズの大幅な抑制に成功

- スマートフォンやスーパーコンピュータなどの種々の電子機器の高性能化と省電力化に向け大きく前進

概要

東京科学大学(Science Tokyo) 総合研究院 WOWアライアンス異種機能集積研究ユニットの大場隆之特任教授と中條徳男特任教授は、WOWアライアンス[用語1]との共同研究により、チップを高速に高精度で実装するChip on Wafer(COW)[用語2]技術および、それを用いた3次元実装されたチップへの電源供給技術を開発しました。

モバイル・ウェアラブル機器から高性能コンピューティング(HPC)の分野に至る幅広い分野において、多くのデータを省エネルギーで伝送させるために、半導体チップを高密度に実装する技術が求められています。しかし、はんだバンプ[用語3]を用いて半導体チップを平面(2次元)に並べる従来のSystem-in-Package(SiP)[用語4]ではバンプやチップの間隔を縮めることが困難でした。私たちは、このような課題を解決するため革新的2.5次元/3次元実装技術、BBCubeTM[用語5]を提案しています。今回、このBBCubeTMの実用化を大きく前進させる、三つの技術を開発しました。

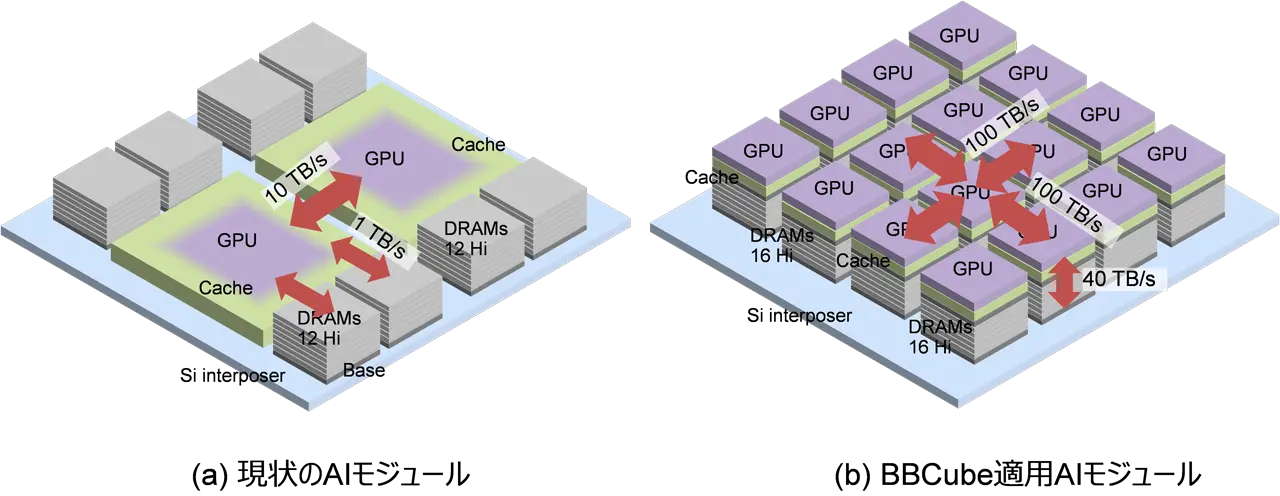

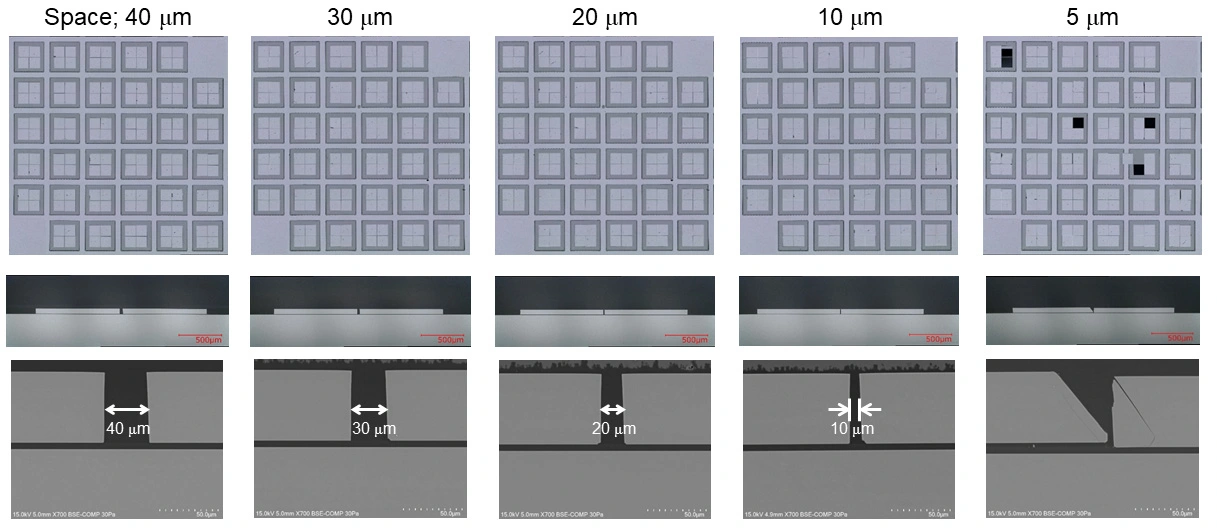

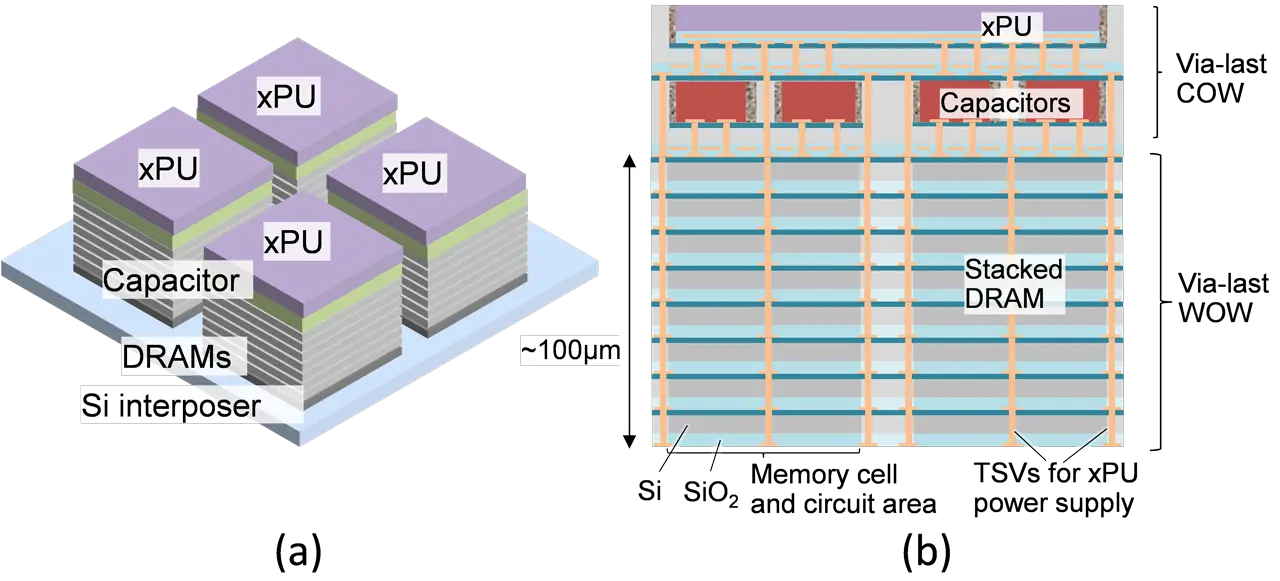

第一は、高速性と高精度を両立したChip-on-Wafer(COW)プロセスの開発です。直径300 mmのワッフルウェーハ[用語6]上に3万個超のチップを10 ms以下で実装でき、チップ間距離をわずか10 µmまで縮めることができました。第二は、COWプロセスやWafer-on-Wafer(WOW)[用語7]プロセスで使われる新規接着剤「DPAS300」の開発です。従来必要だった表面処理剤をなくすことで片面の塗布で済み、チップのような小型な部品の接着も可能にしました。第三は、3次元実装に向けの新しい電源供給技術の開発です。高密度に実装したコンデンサの層をCPUやGPUなどの演算チップと積層したメモリとの間にはさむことで、電源の雑音を演算チップの動作に支障を与えない50mV以下に低減可能なことを明らかにしました。

本成果は、2025年5月27~5月30日開催の電子部品実装に関する国際会議「2025 IEEE 75th Electronic Components and Technology Conference (ECTC)」で3件の発表として報告されました。

背景

半導体の微細化に対する要請は高まる一方であり、その分野はスマートフォンやスマートウォッチなどのモバイル・ウェアラブル機器から人工知能(AI)やスーパーコンピュータを支える高性能コンピューティング(HPC)にまで広がっています。微細化の実現に向けては、半導体チップをパッケージ上に隣接して配置、または積層することで、高密度化、高性能化のトレンドを維持しようとしています。それにはチップ間を大容量で、しかも省エネルギーで伝送することが必要です。しかし、はんだバンプを用いてチップを平面(2次元)に並べる従来のSystem-in-Package(SiP)では、バンプ形状の制御が困難なため、バンプの間隔は最小でも35 µm程度、チップ間隔は80 µm程度にとどまっていました。また、2次元に配置するため、信号はチップの周囲からしか取り出せず、信号線数も制限されていました。このためデータ伝送の大容量化や低消費電力化が難しくなっていました。

私たちは、このような課題を根本的に解決する革新的な2.5次元/3次元実装技術としてBBCubeTMを提案しています。BBCubeTMによりバンプの間隔は10 µm以下にでき、信号線数を従来の4倍以上に増やすことが可能です。WOWアライアンスではBBCubeTMの実用化に向けて、量産に耐えるシンプルな工程と、それを支える材料、そしてチップの高信頼な動作を確保する電源供給技術の確立を目指してきました。

研究成果

本研究では BBCubeTM 実用化の鍵となる三つの技術を開発しました。

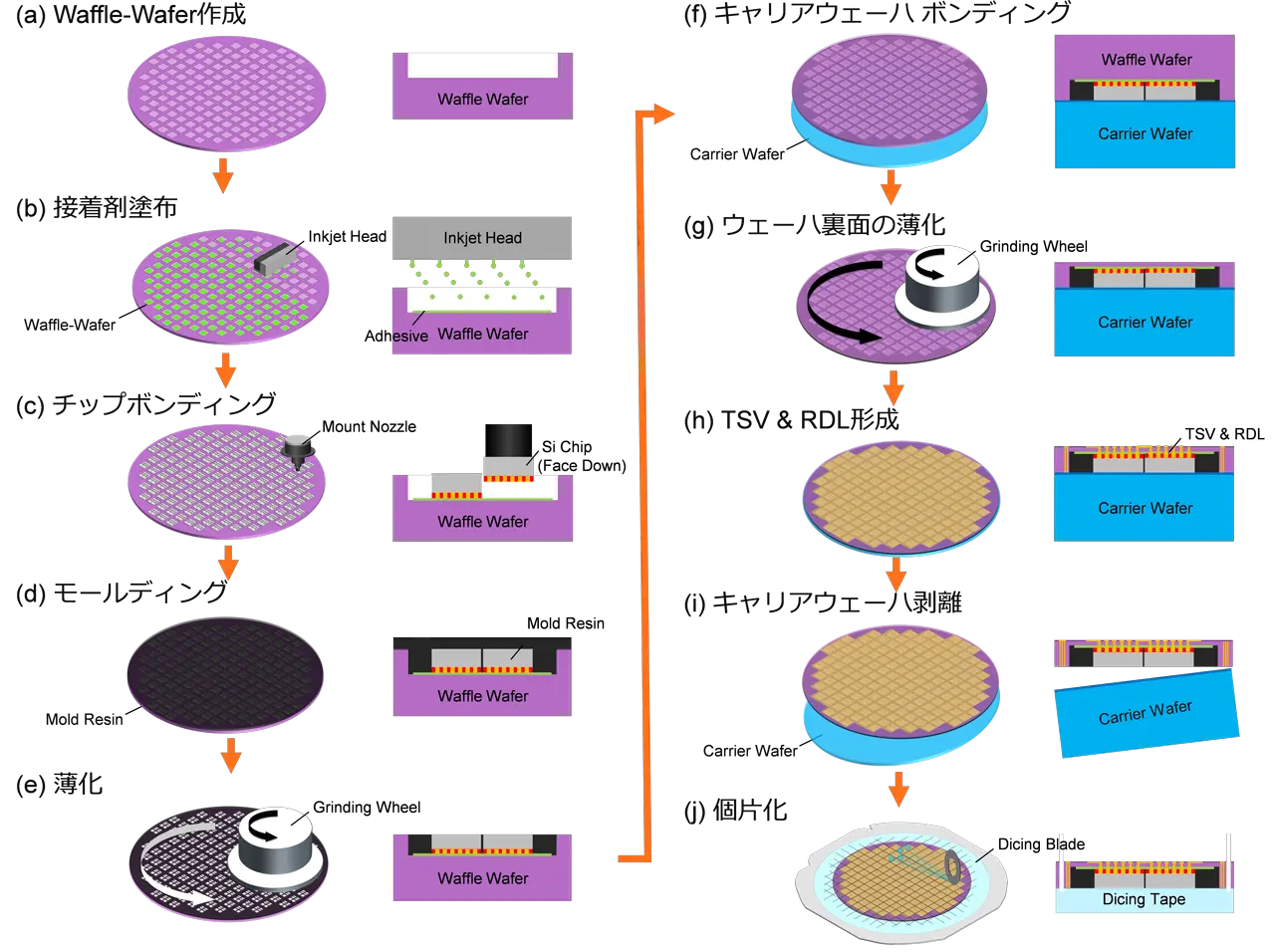

第一の成果として、シンプル低コストな量産工程につながる技術である、Chip-on Wafer(COW)プロセスを開発しました。COWプロセスにおいては、ワッフルウェーハに厚さ 5 µm の接着剤をインクジェットで選択塗布し、高速マウンタでチップを裏向きに実装します。紫外線による部分硬化と 2 段階熱硬化を最適化した結果、チップ間隔 10 µm の超高密度でも剥離を生じず、1 チップ当たり10 ms以下という従来の20倍以上のスループットでチップを搭載できることを実証しました。

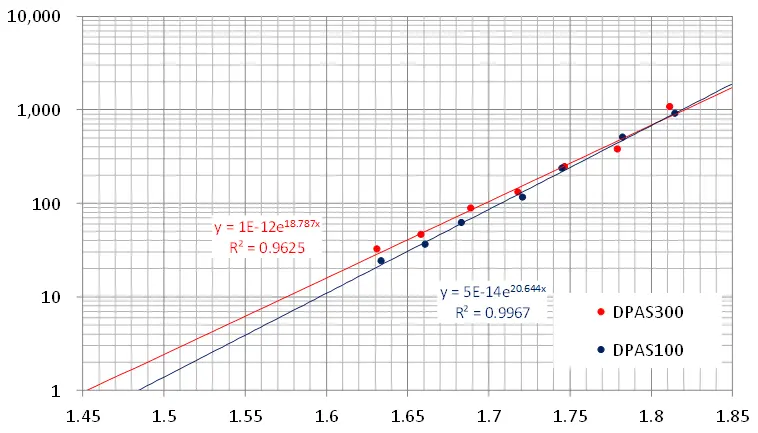

第二の成果は、COW/Wafer-on-Wafer(WOW)の両方のプロセスに使える常温接合型永久接着剤「DPAS300」の開発です。DPAS300はBBCubeTMの製造工程を支える接着材料です。SiOC 系ハイブリッド樹脂に活性官能基をppmオーダーで組み込み、表面改質剤を不要としたことで、片面塗布・室温圧着が可能になり、直径300 mmのウェーハだけでなく数mm×数mmのチップの接着を実現することができました。130℃で前硬化、170℃で完全硬化させても樹脂膨張はCOWの高精度な実装に支障のない5 %未満に抑えられ、−55℃〜150℃ の温度サイクル試験を1,000回行った後も、チップとウェーハの界面に剥離は確認されませんでした。耐熱性に関しては、320℃の環境に60分間さらしても、まで質量変化は1 %未満という優れた安定性を示しています(図3)。

第三の成果は、COW 技術で実装した高密度コンデンサ層を演算チップと多層 DRAMの間に挟み込む新しい電源供給アーキテクチャです(図4)。直径 4 µm、ピッチ 10 µm の シリコン貫通電極(TSV) を DRAM チップの周囲やワッフルウェーハの凸となっている部分に配置し、高密度コンデンサ層と組み合わせることで低抵抗の「Power Distribution Highway」を構築しました。三次元電磁界解析と回路シミュレーションの結果、50 W/cm² 級の最新のGPU を積層したメモリ上に搭載しても、電圧ドロップとスイッチング時のドロップの合計を GPUの動作に支障を生じない50 mV 以下に抑えられることを明らかにしました。

社会的インパクト

半導体は経済安全保障や社会インフラの要となっており、微細半導体工場の建設が各国で進められようとしています。一方で半導体の微細化は限界を迎えつつあり、複数のチップをまとめる実装技術が次の競争力となろうとしています。BBCubeTMは接続密度、接続信頼性、低電力データ伝送、高効率冷却など種々の面で従来の方法に対して優位性を持っています。今回の技術によって、BBCubeTMの量産、システム設計の両面で実用化に向け大きく前進させることができました。

今後の展開

BBCubeTM技術に基づく次世代三次元集積向け製造ラインの構築をテック・エクステンション、ジャパンディスプレイと進めており、2025 年度下期に 300 mm パイロットラインで量産実証を開始する予定です。2.5次元、3次元集積技術の基礎開発だけでなく社会実装も進め、ポスト微細化の実現を目指してまいります。

用語説明

- [用語1]

- WOWアライアンス:WOWアライアンス:東京科学大学総合研究院 WOWアライアンス異種機能集積研究ユニット(大場研究室)が中心となって運営される産学研究プラットフォーム。半導体関連の設計・プロセス・装置・材料などを手がける企業、および研究機関によって構成される。三次元開発としては国内唯一300ミリウェーハを利用した実証開発、高度かつ簡便なウェーハの薄化技術・積層技術を持ち、バンプレスTSV配線を用いた三次元化技術を世界で初めて開発に成功した。

- [用語2]

- Chip-on-Wafer (COW):半導体チップをウェーハ上に接合しながらWOW技術で接続配線する技術。半導体チップをトレンチ加工したウェーハ(ワッフルウェーハ)上に接合することにより、以降の半導体製造工程において、各種ウェーハプロセス装置を用いた高精度な配線加工が行えるようになる。異なるチップサイズの接合も行えることから、サーバーなどの大規模演算2.5Dシステムだけでなく、搭載される異種機能デバイスシステムを超小型化で三次元集積することが可能になる。

- [用語3]

- はんだバンプ:半導体チップと基板やパッケージ、半導体チップ同士を接続するための突起状の電極。熱と圧力を加えてはんだを溶かしながら接続するため、変形したバンプが隣接するバンプと接触してショートしないよう、一定の間隔が必要。

- [用語4]

- System-in-Package (SiP):複数の半導体チップを1つのパッケージにまとめて集積する技術。半導体の微細化が困難になってきていることから、複数の半導体チップをパッケージやインターポーザ上で接続してより大きな処理能力を実現するなど、最新のCPU、GPUで広く使われるようになってきている。

- [用語5]

- BBCube(Bumpless Build Cube):従来の平置きチップレットを三次元でコンパクトにまとめ、バンプを利用しないでシステムの小型化を可能にするアーキテクチャー。参考:Ohba, T.; Sakui, K.; Sugatani, S.; Ryoson, H.; Chujo, N. Review of Bumpless Build Cube (BBCube) Using Wafer-on-Wafer (WOW) and Chip-on-Wafer (COW) for Tera-Scale Three-Dimensional Integration (3DI). Electronics 2022, 11, 236. DOI:/10.3390/electronics11020236

- [用語6]

- ワッフルウェーハ:その名の通り菓子の「Waffle」を由来としたウェーハ表面の加工形状で、ウェーハ表面に四角い溝を規則的にエッチング加工したものである。ドライエッチングの最適化で幾何学的な段差と平坦な底部を形成し、接着層を塗布後、底部にチップをFace-down でボンディングする。ボンディングが完了したらモールディングし、モールド材料とチップ裏面のシリコンを同時に研削、そして平坦化する。チップで専有された四角い溝の残りがモールド体積となる。

- [用語7]

- Wafer-on-Wafer(WOW):ウェーハ上にウェーハを接合する技術。COWと同様の技術であるが、多くのチップが形成されたウェーハ同士を接合することにより、同時に多数のチップの積層ができ、COWよりも効率よい。ただしチップのサイズは同一である必要があるため、メモリ等同一チップを積層する場合に向く。

論文情報

- 学会名:

- 2025 IEEE 75th Electronic Components and Technology Conference (ECTC)

- 日程:

- 2025年5月27-30日

- タイトル:

- (1)Face-Down Bonding and Heterogeneous Chiplet Integration by Using Bumpless Chip-on-Wafer (COW) with Waffle Wafer Technology

著者:Yoshiaki Satake, Wataru Doi, Hajime Kato, Shogo Okita, Tatsuya Funaki and Takayuki Ohba - タイトル:

- (2)Advanced Resin Material Enabling Room-Temperature Bonding for WOW and COW 3DI Applications

著者:Naoko Araki, Tadashi Fukuda and Takayuki Ohba - タイトル:

- (3)BBCube 3D: Fully Vertical Heterogeneous Integration of DRAMs and xPUs using a New Power Distribution Highway

著者:Norio Chujo, Hiroyuki Ryoson, Koji Sakui, Shinji Sugatani, Masao Taguchi and Takayuki Ohba

研究者プロフィール

大場 隆之 Takayuki Ohba

東京科学大学 総合研究院 WOWアライアンス異種機能集積研究ユニット 特任教授

研究分野:BBCube三次元大規模集積技術および応用技術

中條 徳男 Norio Chujo

東京科学大学 総合研究院 WOWアライアンス異種機能集積研究ユニット 特任教授

研究分野:BBCube3次元集積のデザイン、アーキテクチャ

関連リンク

更新履歴

- 2025年9月1日 組織名の誤記を修正しました。