ポイント

- 高精度なFMCWレーダー用チャープ信号を生成する低消費電力CMOS ICを開発

- 発振器の周波数誤差を回路内部で自己補償する新規アーキテクチャを採用

- 通信とセンシングを同時に行う新周波数帯FR3を活用した6G ISAC向けエッジ/IoTデバイスへの応用に期待

概要

東京科学大学(Science Tokyo)工学院 電気電子系の岡田健一教授らの研究チームは、周波数掃引が高い線形性を持つよう、周波数誤差を回路内部で補償する自己線形化電圧制御発振器(VCO[用語1])を用いて、新しいFMCWレーダー[用語2]用信号発生器を開発しました。

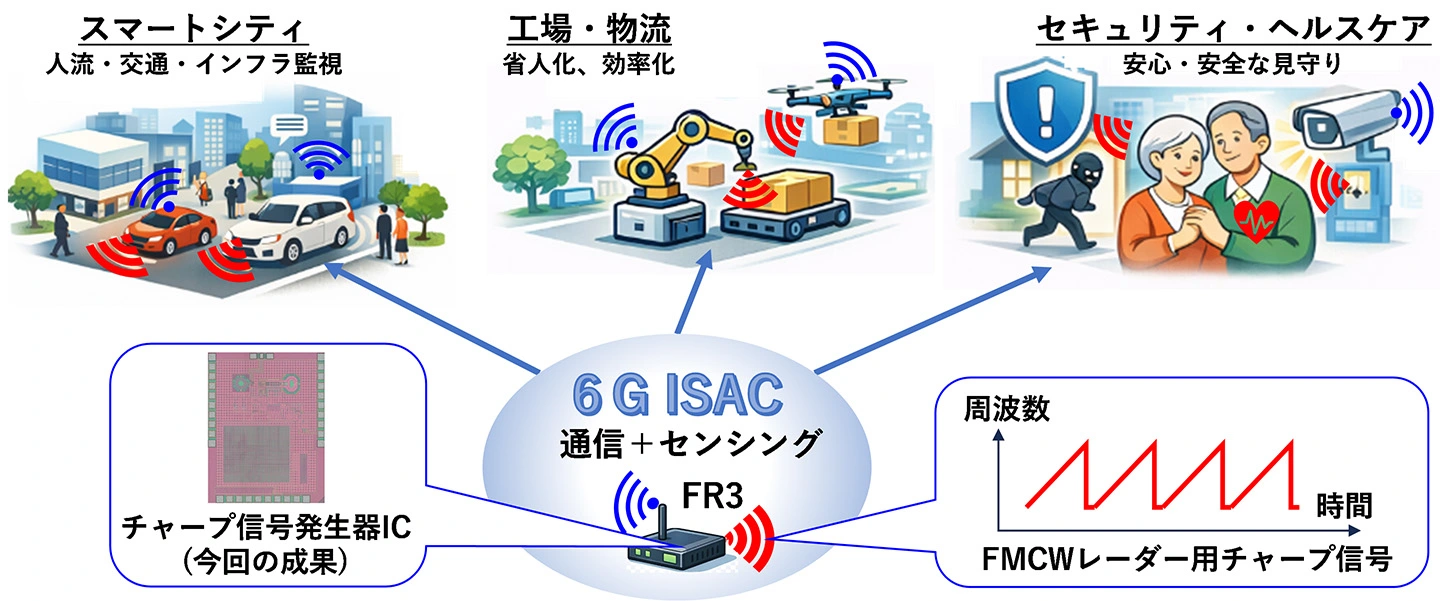

近年、Beyond 5G/6G[用語3]に向けた次世代無線通信の研究開発が進む中、通信とセンシングを同時に行うISAC[用語4]が注目されています。特に、高速通信と高精度センシングに適した6G向け新周波数帯FR3[用語5]を活用したISACは、スマートシティや産業IoT、インフラ監視など、さまざまなエッジ/IoT デバイスへの展開が期待されています。ISACでは、無線通信機器が周囲環境を高精度に把握する必要があり、その実現には高性能なFMCWレーダー技術が不可欠です。しかし、従来の高性能FMCWレーダー用信号発生器は回路規模が大きく、小型・低消費電力なSoC[用語6]として実装することが困難であるという課題がありました。

本研究では、VCOの非線形性を回路内部で自己補償することにより、FMCWレーダーにおいて高分解能に必要な「高速・広帯域」と、高精度測定に必要な「高線形性」を同時に満たすチャープ信号[用語7]を生成する新しい回路方式を提案しました。65 nm CMOSプロセスで試作したICは、最大チャープレート1.56 GHz/μs、帯域1 GHz、周波数誤差0.1%未満、消費電力9.8 mWという世界最高水準の性能を実証しています。

本研究は、次世代モビリティと6G時代のセンシング基盤を支える中核技術として、今後の社会実装とさらなる技術革新が期待されます。

本成果は、2月15日~19日(米国太平洋時間)に米国サンフランシスコで開催される「2026 IEEE International Solid-State Circuits Conference(ISSCC、国際固体素子回路会議)」で発表されます。

背景

近年、6Gに向けた次世代無線通信の研究開発が進む中で、FR3と呼ばれる新しい周波数帯を利用した通信とセンシングの融合(ISAC:Integrated Sensing and Communication)が重要な技術として注目されています。6Gでは、無線通信機器自体が周囲環境を高精度に把握し、通信と同時に距離や速度、物体の存在を検知することが求められており、その実現には高精度なFMCW(Frequency Modulated Continuous Wave)レーダー技術が不可欠です。

ISAC技術は、6Gネットワークにおいて、スマートシティ、インフラ監視、産業IoT、ヘルスケア、ロボティクスなど、さまざまなエッジ/IoTデバイスへの展開が期待されています(図1)。こうした 6G 向けセンシング応用においては、自動車の高度運転支援システム(ADAS)や自動運転技術の進展により培われてきた FMCW レーダー技術が、重要な基盤技術となっています。

しかし、従来の高精度FMCWレーダーは、消費電力や回路規模が大きく、6Gエッジデバイスに求められる小型・低消費電力なSoCとして実装することが困難でした。特に、高分解能センシングを実現するために必要な高速・広帯域な周波数掃引(チャープ)を行うと、電圧制御発振器(VCO:Voltage Controlled Oscillator)の非線形性による周波数誤差が顕著となり、誤検知の増加や電力効率の低下が大きな課題となっていました。

本研究は、こうした課題を解決し、FR3帯を用いた6G ISAC向けの高精度FMCWレーダーを低消費電力SoCとして実装可能とすることを目的として実施されました。これにより、通信とセンシングを同時に行う次世代エッジ/IoTデバイスへの幅広い展開が期待されます。

研究成果

本研究では、自己線形化VCO(Self-Linearized Voltage-Controlled Oscillator)を用いた新しいFMCW用チャープ信号発生器を提案し、CMOS ICとして実証しました。本方式は、従来のFMCW用チャープ信号発生器において大きな課題であった「チャープレート(周波数掃引速度)」と「線形性(周波数誤差)」のトレードオフを、回路構造レベルで根本的に解決するものです。

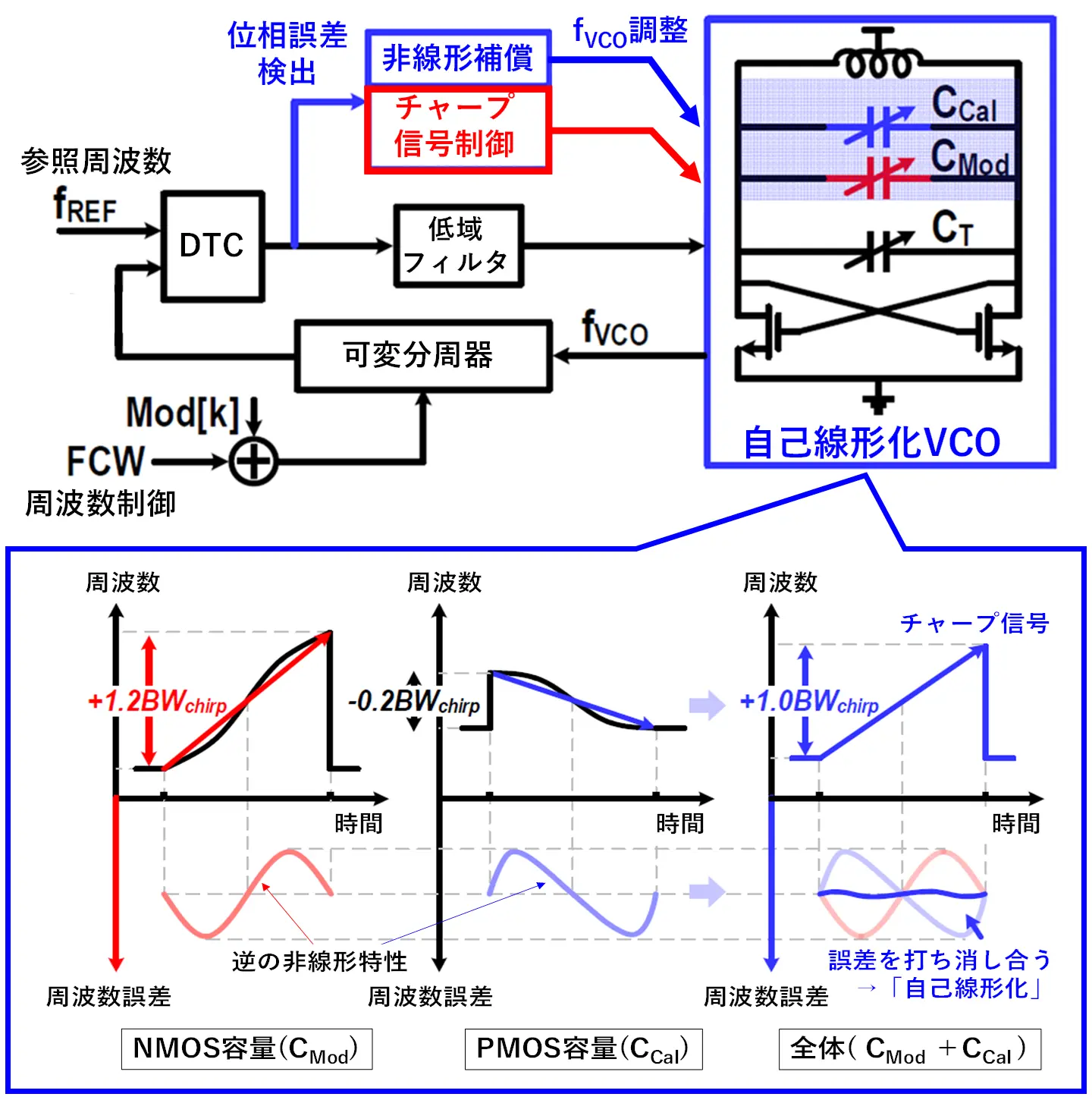

次世代のFMCWレーダーでは、速度分解能および距離分解能を向上させるために、高速かつ広帯域なチャープ信号が求められます。また、高精度なセンシングを実現するためには、チャープ信号に高い線形性が必要です。従来は、チャープ信号発生器の非線形性を補償する手法として、デジタル非線形補償(DPD:Digital Pre-distortion)技術[用語8]が広く用いられてきました。しかし、チャープ信号が高速・広帯域化すると、デジタル補償に必要なサンプリング点数が不足し、十分な線形性を確保できないという課題がありました。さらに、高い線形性を実現するためにチャープ信号を複数の時間領域に分割して補償する必要があり、その結果、多数(例えば32個や64個)のルックアップテーブル(LUT:Look-up Table)が必要となるため、デジタル部のオーバーヘッドが大きいという課題もありました。

これらの課題に対する提案手法の特徴は、VCO内部のLC共振回路において、チャープ信号を制御する容量(CMod)と、それによって生じる非線形性を補償する容量(CCal)を備えている点にあります。CModはN型MOS容量、CCalはP型MOS容量で構成されており、両者の非線形特性が逆符号であることから、VCOの非線形性を回路内部で自己補償することが可能です(図2)。さらに、CCalによりチャープ信号の傾きとオフセットを調整することでVCOの非線形性を補償できるため、必要なLUTは2つのみで済みます。その結果、従来技術と比べて極めて低いデジタルオーバーヘッドで、高精度かつ高速・広帯域なFMCWチャープ生成を実現できます。

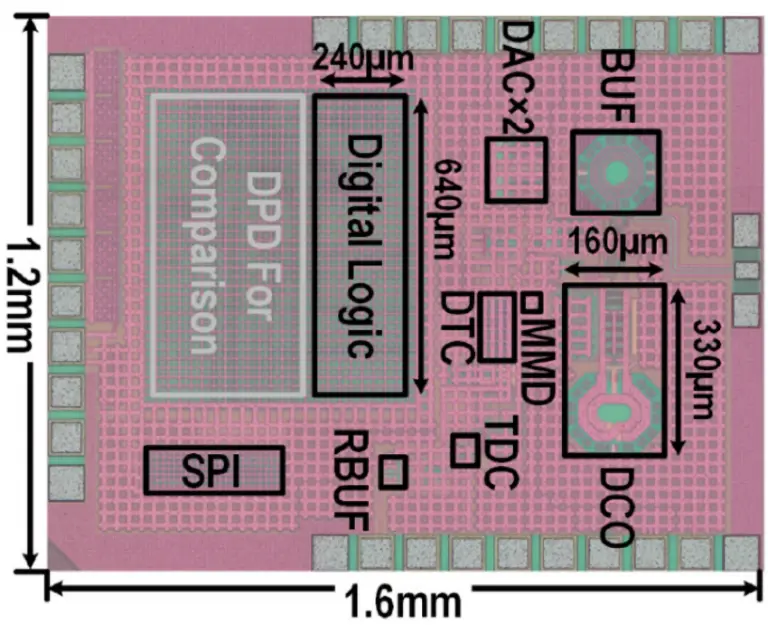

提案したFMCW用チャープ信号発生器を、65 nm CMOSプロセスを用いて試作しました。チップサイズは、1.6 mmx1.2 mmです(図3)。試作したICは、以下の優れた性能を実証しています。

- 最大チャープレート:1.56 GHz/μs

- 最大チャープ帯域:1 GHz

- リトレース時間:40 ns

- 周波数誤差(rms):0.1%未満

- 消費電力:9.8 mW

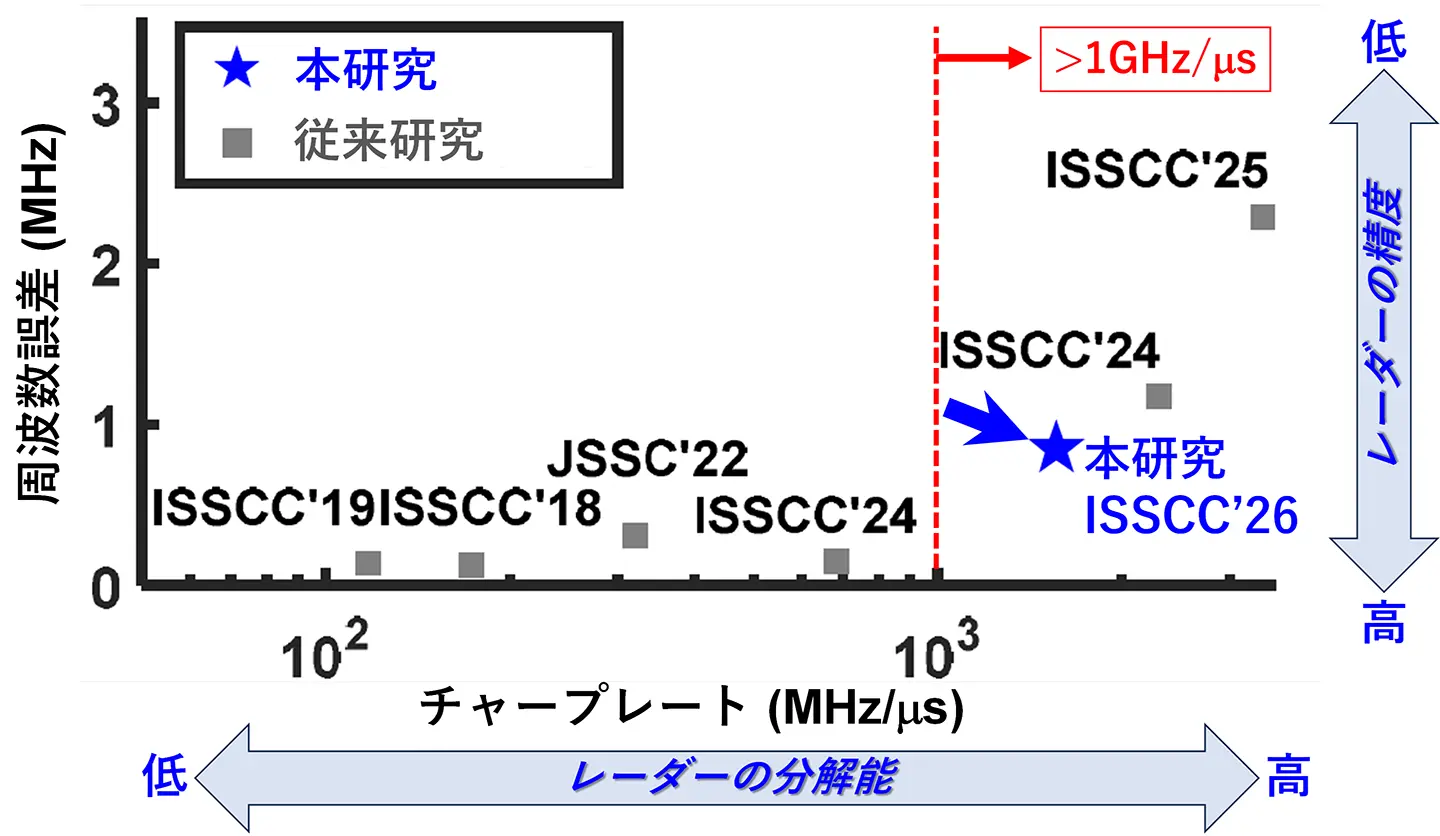

これらの性能は、SoC搭載を前提とした低消費電力動作を維持しながら、従来方式では困難であった高速・広帯域・高線形FMCWチャープ生成を実現したことを示しています。さらに、本研究は1 GHz/μs を超える高速チャープ領域において、既存の先行研究と比較して最小の絶対周波数変調誤差を達成している点が特筆されます(図4)。同時に、位相雑音性能についても競争力のある水準を維持しており、高精度センシングと高品質無線信号生成を両立できることを実証しました。

本成果は、高精度・低消費電力を同時に満たすFMCWレーダー回路技術として、B5G/6GにおけるFR3を活用したISAC向けエッジ/IoTデバイスへの展開を強く後押しするものです。

社会的インパクト

本研究成果により、高精度FMCWレーダーを小型・低消費電力なSoCとして実装する道が開かれました。これにより、これまで高性能レーダーの搭載が難しかった多くのエッジデバイスへの展開が可能になります。

具体的には、

- 6G ISACによる「通信しながら周囲を理解する」小型無線機の実現

- 自動車の安全性向上(高精度な衝突防止・周辺監視)

- スマートシティにおける人流・交通・インフラのリアルタイム監視

- 工場や物流現場での非接触センシングによる省人化・効率化

- 高齢者見守りや医療・ヘルスケア分野での安全・安心の実現

など、人々の生活の安全性・利便性を支える基盤技術として幅広い社会的価値を生み出すことが期待されます。特に、電池駆動のIoTデバイスでも利用可能な低消費電力設計は、持続可能な社会の実現にも大きく貢献します。

今後の展開

今後は、本技術をさらに発展させ、より高い周波数帯(ミリ波・サブテラヘルツ帯)への対応や、通信機能と統合したISAC向けSoCへの展開を進めていく予定です。また、AI処理回路やデジタル信号処理との統合により、センシング情報をその場で解析・判断する「エッジAIデバイス」の実現を目指します。

加えて、産業界との連携を通じて、IoTセンサ、6G小型無線機、車載レーダーなどへの社会実装を加速させ、研究成果を実際の製品・サービスとして社会に還元していくことを計画しています。

本研究は、次世代モビリティと6G時代のセンシング基盤を支える中核技術として、今後の社会実装とさらなる技術革新が期待されます。

付記

本研究成果は、国立研究開発法人情報通信研究機構(NICT、エヌアイシーティー)の委託研究(JPJ012368C00801)により得られたものです。

用語説明

- [用語1]

- VCO(Voltage Controlled Oscillator):電圧制御発振器。入力電圧の値を変えることで、出力信号の周波数を変化させることができる電子発振回路。

- [用語2]

- FMCW(Frequency Modulated Continuous Wave)レーダー:周波数連続変調波レーダー。時間とともに周波数が変化する電波(チャープ信号)を連続的に送信し、反射波との周波数差や位相差を測定することで、対象物までの距離や速度を検出するレーダー方式。

- [用語3]

- Beyond 5G/6G:Beyond 5Gは、第5世代移動通信システム(5G)以降の移動通信システムの総称。2030年頃の導入が予定されている次の世代を特に6Gと呼ぶ。

- [用語4]

- ISAC(Integrated Sensing and Communication):通信と電波による物体検知(センシング)を1つのシステムに統合する技術。6Gでの導入に向けて、3GPP等で検討が行われている。

- [用語5]

- FR3(Frequency Range3):5Gで利用されるFR1(サブ6GHz帯)とFR2(ミリ波)の中間に位置する7.125–24.25 GHzの周波数帯(センチメートル波)。6Gの候補周波数として、ITU(国際電気通信連合)で検討が進んでいる。

- [用語6]

- SoC(System on Chip):1つのチップ上に、システムを構成する複数の機能を集積した半導体集積回路。

- [用語7]

- チャープ(Chirp)信号:周波数が時間とともに直線的に増加する(または減少する)電波信号。

- [用語8]

- デジタル非線形補償(DPD:Digital Pre-distortion)技術:信号の非線形性を補償するための技術。対象となる回路の非線形性をモデル化し、その逆特性の信号を入力することで、線形な出力信号を得る。

論文情報

- 発表学会:

- 2026 IEEE International Solid-State Circuits Conference(ISSCC)

- 講演セッション:

- Session 27 - Frequency Generators, Multipliers, and Modulators

- 講演時間:

- 現地時間2月18日午前10時05分

- タイトル:

- A 9.7GHz Self-Linearized-VCO-Based FMCW Chirp Generator Achieving 1.56GHz/μs Slope and 0.57μs Duration with 0.094% rms Frequency Error

- 著者:

- Daxu Zhang, Yuncheng Zhang, Zezheng Liu, Yuang Xiong, Michele Rossoni, Wenqian Wang, Ashbir Aviat Fadila, Duo Li, Minzhe Tang, Dongfan Xu, Carrel de Gomez, Dingxin Xu, Kazuaki Kunihiro, Hiroyuki Sakai, Kenichi Okada

ISSCC 2026 会議情報:

学会サイト:ISSCC - International Solid-State Circuits Conference

プログラム:ISSCC Program Overview

研究者プロフィール

岡田 健一 Kenichi Okada

東京科学大学 工学院 電気電子系 教授

研究分野:無線機・高周波回路(RFアナログ回路、ミックスドシグナル回路)

関連リンク

更新履歴

- 2026年4月1日 DOIを追記しました。