ポイント

- 次世代半導体チップやメモリの実現に向けた半導体材料・デバイス・プロセス技術を開発

- ALD法を用いて超極薄膜のpoly-IGOナノシート酸化物半導体を合成

- poly-IGOナノシートをチャネル層に用いたFETにおいて、120 cm2/Vsを超える真性電界効果移動度を達成

概要

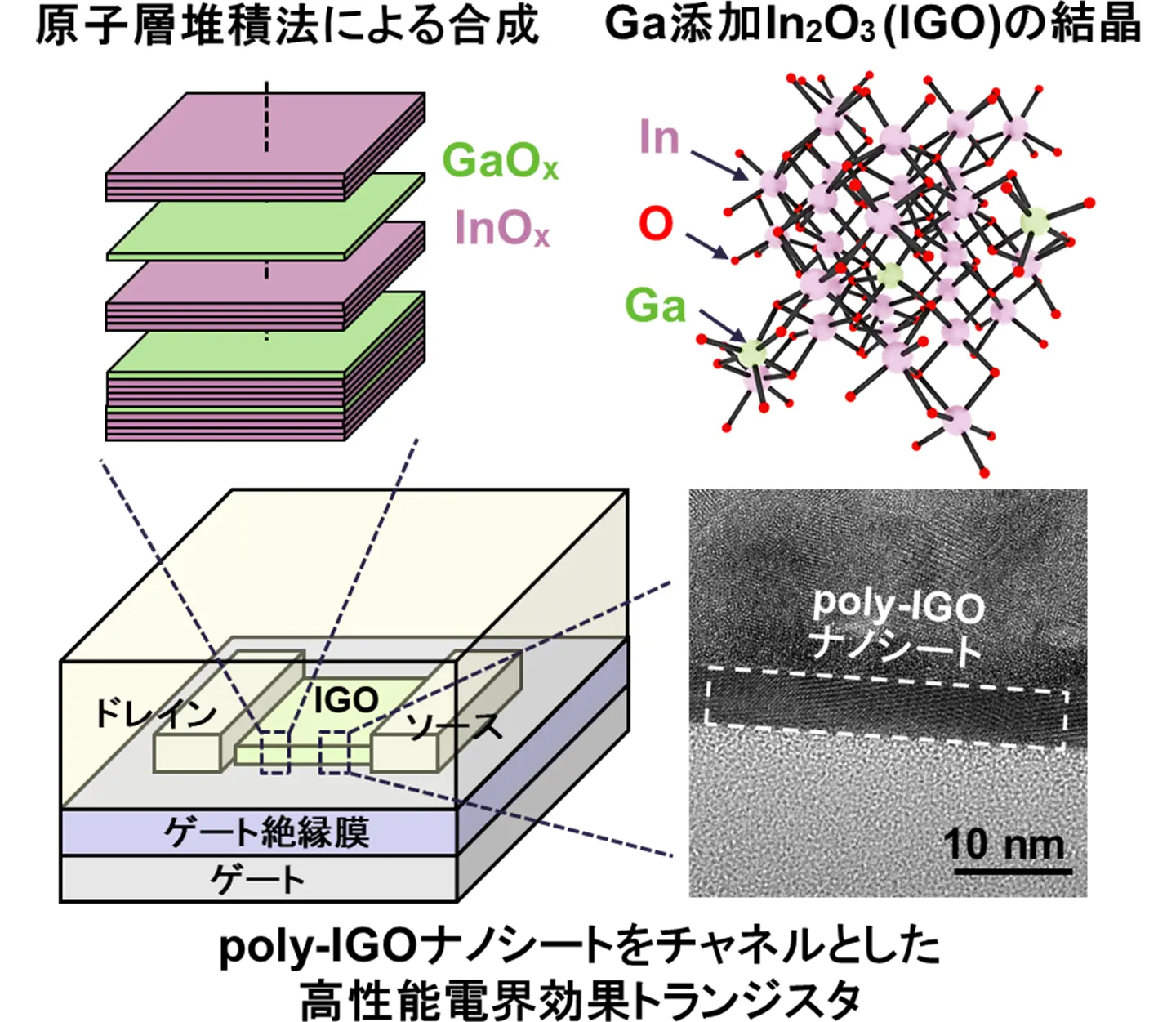

東京科学大学 工学院 電気電子系 角嶋 邦之 准教授、星井 拓也 助教、奈良先端科学技術大学院大学 先端科学技術研究科 物質創成科学領域の髙橋 崇典 助教、浦岡 行治 教授、出光興産株式会社 らによる共同研究グループは原子層堆積(ALD)法[用語1]を用いることで高性能かつ高機能な多結晶酸化物半導体Ga添加In2O3(poly-IGO :polycrystalline Ga-doped In2O3)ナノシートとそれをチャネルに用いた電界効果トランジスタ(FET)[用語2]の開発に成功しました。

本研究では各機関が有する半導体材料・デバイス、プロセス、薄膜合成手法の知見を集結して半導体集積回路や半導体メモリの基盤技術となり得る高性能化かつ高機能な酸化物半導体[用語3]材料とFET技術の開発に取り組みました。ALD法を用いることで超極薄膜の高品質なpoly-IGOの合成が可能になり、これをFETのチャネル層に適用しました。その結果、5 nm以下の極めて薄いpoly-IGOをチャネルに用いたFETは真性電界効果移動度[用語4]120 cm2/Vsを超える高い性能を達成しました。さらに、標準材料であるIn2O3に対してGaを添加することで、薄膜の加工性および電気的特性が改善することも明らかになりました。本技術は半導体デバイスの更なる高性能化・高集積化・低消費電力化に寄与するものであり、次世代半導体チップやメモリデバイスの実用化に向けた重要なステップになることが期待されます。

本研究成果は、2025年6月6日から12日に京都市で開催される国際会議「2025 Symposium on VLSI Technology and Circuits」で発表されます。

背景

現代の情報社会では大量のデータが日々生成・活用され、私たちの暮らしを支えています。その基盤となるのが半導体技術であり、情報の演算、記憶、通信、表示などあらゆる場面で使われています。IoTやAIなどの先端情報技術が急速に広がる中、半導体チップにはより高性能で小型かつ低消費電力な設計が求められています。こうしたニーズに応えるため、近年では半導体チップの後工程(BEOL)にも高機能な半導体回路や半導体メモリを三次元方向に積み重ねる技術開発が進められています。そのためには、400 ℃程度の低温プロセスで高性能な半導体材料を合成し、それを用いたFETを作製する必要があります。In2O3、ZnO、In-Ga-Zn-Oなどの酸化物半導体は、比較的低温でも高い性能が得られ、漏れ電流が小さい特長を持っており、従来のディスプレイ分野だけではなく次世代半導体デバイスの有力材料として注目されています。しかし、一般的な非晶質構造[用語5]を持つ酸化物半導体では膜厚を薄くすると電子移動度が低下してしまいFETの性能が十分に発揮できない課題もあり、より高性能を発揮できる材料への技術要求がありました。

そこで本研究では、高い電子移動度を達成できる可能性がある多結晶構造[用語6]を持つ酸化物半導体のGa添加In2O3(IGO, Indium Gallium Oxide, Ga-doped In2O3)に注目しました。共同研究者の出光興産株式会社は2006年よりIGOの開発を始め、スパッタリングターゲットの実用化技術を開拓しました。しかし、集積半導体応用においては従来のスパッタリング法[用語7]を用いた薄膜合成には技術的な限界があったため、三次元構造体により薄く均一で高品質な薄膜を成長できるALD法を用いたpoly-IGOナノシートの合成と高性能FETの開発を進めました。

研究の内容

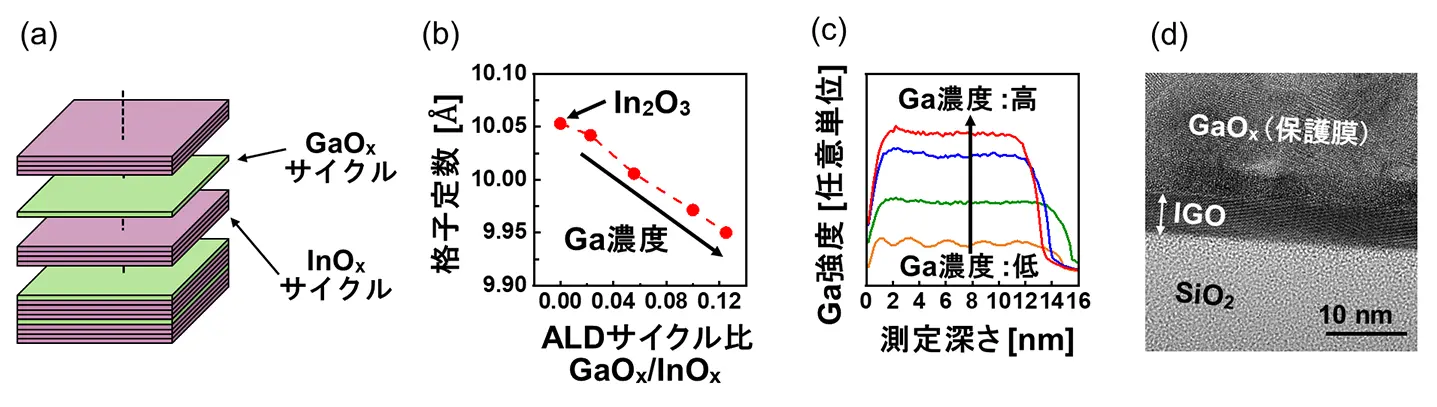

ALD法を用いたIGO薄膜はInOx層とGaOx層の原子層レベルで交互に積み重ねていくことで合成することができます(図1-a)。成膜中のGaOx層の成長割合を増やすと結晶の格子定数[用語8]が減少し、In2O3結晶中のInの一部がGaに置き換わっていることが確認されました(図1-b)。この結果はInOx層とGaOx層が結晶化する時に互いに混ざり合っていることを示しており、均一なpoly-IGO薄膜を合成することに成功しました(図1-c)。この薄膜は約5 nmという極めて薄い状態でも完全に結晶化しており、高品質なナノシートが実現できました(図1-d)。

(a)ALD法によるIGO薄膜の成長概念図。

(b)IGO薄膜の格子定数とALDサイクル比:GaOx/InOxの関係。結晶中のGaイオンはInイオンよりも小さいため、ALDサイクル比が増加すると薄膜中のGa濃度が上昇することで結晶格子が小さくなりIGO薄膜の格子定数は減少する。

(c)異なるALDサイクル比で合成したIGO薄膜におけるGaの深さ濃度分析結果。ALDサイクル比とGa濃度を最適化することで膜厚方向・測定深さ方向にGaが均一に分布したIGO薄膜が得られる。

(d)IGO薄膜の断面透過電子顕微鏡画像。約5 nmの結晶構造を有するIGOナノシートが成長していることが確認された。

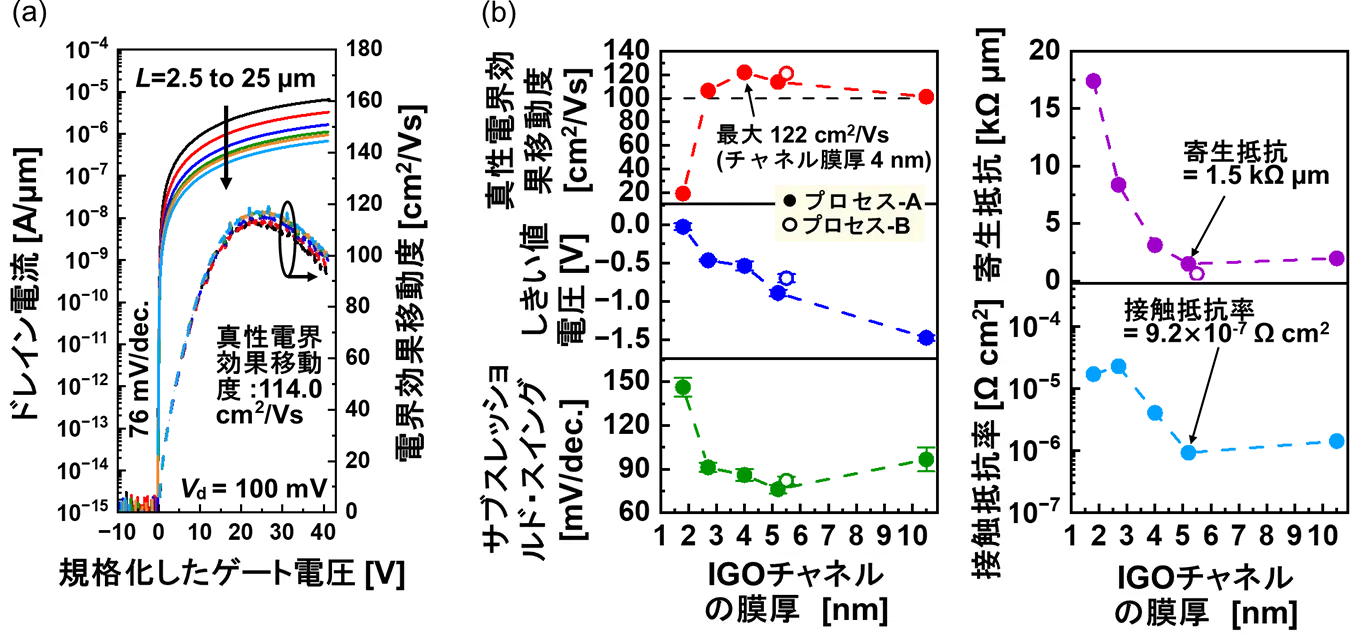

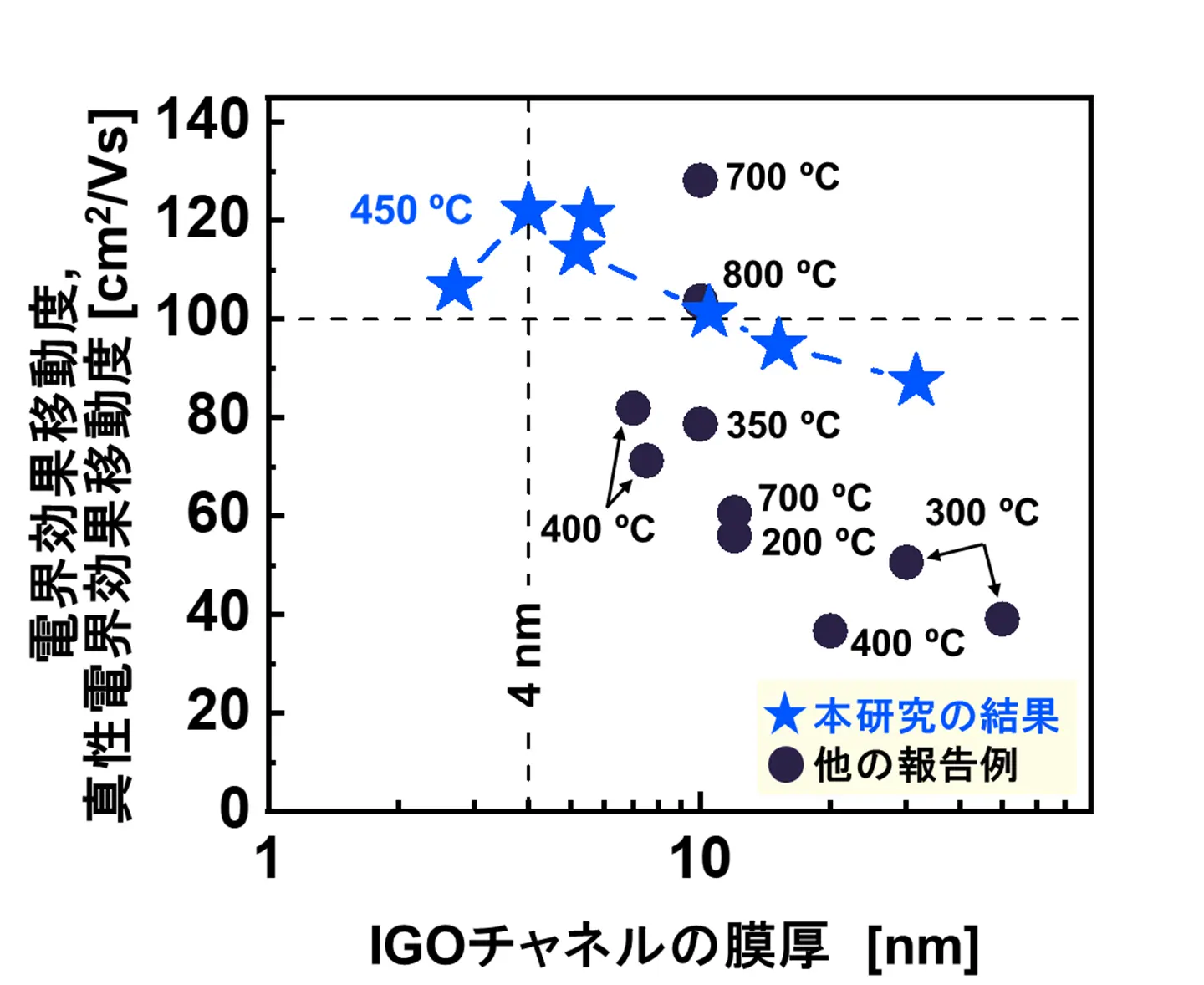

poly-IGOナノシートを用いて試作したFETは、真性電界効果移動度114 cm2/Vs、サブスレッショルドスイング[用語9]76 mV/decadeという高性能を示しました(図2-a)。この真性電界効果移動度の値は従来材料の5~10倍以上の値です。また、チャネル膜厚を3 nmまで薄くしても、100 cm2/Vs以上の高い真性電界効果移動度が維持されており(図2-b)、微細な半導体デバイスにも対応可能です。さらに、チャネル膜厚と作製プロセスを最適化することによって、122 cm2/Vsという世界最高レベルの真性電界効果移動度と10-7Ω cm2台の低い接触抵抗率[用語10]も実現しました。他の報告例と比較したところ、本研究のpoly-IGOは5 nm以下という極薄膜のナノシート領域でも高い性能を保てること、そしてBEOL応用を想定した450 ℃以下の低温プロセスで作製可能な点が大きな強みであることが分かりました(図3)。

(a)作製したpoly-IGOチャネルFETの伝達特性と算出した電界効果移動度。伝達特性のチャネル長依存性を評価することで真性電界効果移動度や寄生抵抗、接触抵抗率を算出した。

(b)poly-IGOチャネルFETから抽出した真性電界効果移動度、しきい値電圧、サブスレッショルドスイング、寄生抵抗、接触抵抗率とチャネル膜厚の関係。本研究のpoly-IGOはチャネル膜厚のスケーリング特性が優れており、作製プロセスや膜厚を制御することで更なる性能向上も期待できる。

今後の展開

本研究により、ALD法を用いて高品質なpoly-IGOナノシートを合成できること、poly-IGOナノシートが高い電子移動度と低い接触抵抗率を持つことが明らかになりました。また、論文では材料物性や薄膜の加工性、高真性電界効果移動度が達成できる理由についても分析しています。今後は、さらなる性能向上や信頼性の確保に向けて、より優れた材料やプロセスの開発を進めます。そして、本技術を三次元構造のFETやメモリデバイスなどへ展開し、酸化物半導体の実用性を半導体集積回路全体に広げていくことを目指します。

研究助成

本研究の一部は日本学術振興会 科研費(23K19123)および文部科学省 次世代X-nics半導体創生拠点形成事業(JPJ011438)の支援を受けて実施されました。

用語説明

- [用語1]

- 原子層堆積(ALD)法:化学反応を用いて薄膜を合成する手法であり、真空容器中に基板を設置し、得たい化合物の原料と反応剤の供給時間をそれぞれ別々に緻密に制御することで薄膜を合成することができる。金属と酸素の化合物を合成する場合、原料として有機金属化合物、反応剤として水、オゾン、酸素のプラズマなどが用いられる。ALD法は薄膜または基板の表面の化学反応が起点となって薄膜が合成されるため、二次元平面だけではなく、三次元の複雑な構造物の上であっても均一な薄膜合成が可能であり、段差被覆性に優れる特徴がある。さらに理想的には原子層毎に薄膜が成長していくため、薄膜の厚さを精密に制御することができる。

- [用語2]

- 電界効果トランジスタ(FET):半導体デバイスの一種であり、ゲート・ソース・ドレインの3つの電極と半導体、絶縁体薄膜によって構成される。FETのゲート電極に印加する電圧を調整することで、半導体の中のキャリア(電子)の量を変化させることでソース・ドレインの間に流れる電流を制御することができる。FETはほぼ全ての半導体チップや電子デバイスの中に組み込まれている。

- [用語3]

- 酸化物半導体:金属元素と酸素の化合物で半導体の特性を示すものである。その代表例がIn-Ga-Zn-O(IGZOと呼ばれる)やIn2O3:SnO2(ITOと呼ばれる)であり、ディスプレイを駆動するFETの材料や透明電極の材料として実用化されている。一般に酸化物はガラス(シリコンと酸素の化合物)やセラミックスのように電子が流れない絶縁体である物質がほとんどであるが、一部の物質は酸素の一部が欠損することや水素が導入されることで半導体の特性を示すものが存在する。

- [用語4]

- 真性電界効果移動度:物質の中の電子や正孔の移動しやすさを移動度と呼ぶ。この値が大きいほど半導体の性能、FETの特性がよいとされ、FETに応用した際に大きな電流を流すことができる。また、電界効果移動度はFETの電気的特性から計算される移動度であり、本研究ではFET応用時に発生する誤差要因である寄生抵抗や寸法の偏差を補正することで真性電界効果移動度を計算している。

- [用語5]

- 非晶質構造:原子や分子の長距離での秩序的・周期的な配列がなく結晶構造が認められない物質の状態・構造である。非晶質構造を有する材料の例としてガラスなどが挙げられ、半導体材料では非晶質水素化シリコンやIn-Ga-Zn-Oなどが存在する。

- [用語6]

- 多結晶構造:原子や分子の長距離での秩序的・周期的な配列が存在している多数の小さな単結晶の粒が集合し、それぞれが乱雑な方向を向いている結晶の状態・構造である。多くの金属材料やセラミックス材料は多結晶構造であり、半導体材料では多結晶シリコンやIn2O3:SnO2などが挙げられる。

- [用語7]

- スパッタリング法:ALD法とは異なり、物理的な反応を用いて薄膜を合成する手法である。具体的には真空容器中に2つの電極を設けて各電極上に基板と成膜したいターゲット物質をそれぞれ設置する。そこにアルゴン等の希ガスを流し、電極間に高電圧を印加することで希ガスのプラズマを発生させ、電圧によって希ガスイオンをターゲット物質に衝突させる。その際にターゲット物質からたたき出された物質を基板上に堆積させることで薄膜を合成する。たたき出された物質は直線的に基板に向かうるため、二次元平面上では均一な薄膜を合成できる利点があるが、三次元の立体構造への均一な成膜は一般的に難しいとされている。

- [用語8]

- 格子定数:結晶の最小単位である単位格子の結晶軸の長さや角度を示す定数であり、物質固有の値を持つ。本研究では立方晶の結晶材料を扱っているため、材料の構造を立方体と仮定した際の各辺の長さを格子定数としている。

- [用語9]

- サブスレッショルドスイング:FETの性能指標の1つであり、FETがONするしきい値電圧よりも低いゲート電圧領域において、電流が一桁増大するために必要なゲート電圧の量として定義される。この値が小さいほど低い電圧でFETが駆動でき、消費電力も小さくすることができる。

- [用語10]

- 接触抵抗率:FET中の半導体はソースとドレインの電極と接触しており、接触部には抵抗成分が必ず発生してしまう。この抵抗成分を寄生抵抗と呼び、寄生抵抗を十分に小さくすることでFETの特性を引き出すことができる。また、電極材料と半導体材料が接触するときの抵抗成分を接触抵抗率と呼び、十分に小さくする必要がある。

論文情報

- タイトル:

- ALD polycrystalline Ga-doped In2O3 (poly-IGO) nanosheet exceeding intrinsic mobility of 120 cm2/Vs for process-friendly BEOL-compatible FET application

- 著者:

- Takanori Takahashi1, Takuya Hoshiim2, Yuki Tsuruma3, Misa Sunagawa3, Shigekazu Tomai3, Jongho Parkm2, Hiroki Tamamotom2, Kuniyuki Kakushima2, Yukiharu Uraoka3

- 所属:

- 1奈良先端科学技術大学院大学, 2東京科学大学, 3出光興産株式会社

学会情報

- 開催期日

- 2025年6月8日(日)~6月12日(木)

- 開催場所

- リーガロイヤルホテル京都

- 発表日時

- 2025年6月12日(木)午前8時55分(日本時間)

関連リンク

お問い合わせ

奈良先端科学技術大学院大学 先端科学技術研究科 物質創成科学領域 情報機能素子科学研究室

助教 髙橋 崇典

- t.takahashi@ms.naist.jp

- Tel

- 0743-72-6063

取材申込み

東京科学大学 総務企画部 広報課

- media@adm.isct.ac.jp

- Tel

- 03-5734-2975

- FAX

- 03-5734-3661