ポイント

- わずか0.2 V程度の超低電圧で伝達特性のヒステリシス幅を最大限に拡大できる新たなCMOSインバータを提案

- 新型インバータを用いて、超低電圧でも極めて低い不良率を確保し、データを保持できる新しいSRAMセルを開発

- 超低電圧データ保持技術によって、待機時電力を不揮発性メモリ並みに削減可能

概要

東京科学大学(Science Tokyo)総合研究院 未来産業技術研究所の菅原聡准教授、塩津勇作研究員、工学院 電気電子系の伊藤克俊大学院生(研究当時)は、超低電圧でSRAMのノイズ耐性を大幅に向上できる新たなインバータを提案し、これを用いて新しいSRAMのメモリセルを開発しました。

SRAMは、マイクロプロセッサやアクセラレータ[用語1]などのCMOSロジックシステムに用いられる重要な記憶回路です。このSRAMの重要な課題である待機時電力削減を目指し、本研究グループでは、超低電圧でデータを保持(超低電圧リテンション(ULVR)[用語2])することが可能なSRAM(ULVR-SRAM)の研究・開発を進めてきました。

本研究ではまず、伝達特性のヒステリシスをほぼ最大限に拡大できる新型インバータを提案しました。このインバータは、遮断時のトランジスタに生じるリーク電流を用いた擬似nMOSインバータ[用語3]と内部に特殊なフィードバックの構造を有します。このインバータで双安定回路を構成したSRAMセルは8つのトランジスタで構成できます(8TUセル)。次に、セルを構成するトランジスタのプロセス(グローバル/ローカル)ばらつきを考慮した8TUセルの設計方法を開発しました。最適設計された8TUセルはランダムなローカルばらつき下でも全動作モードで6σの不良率を満足できる十分なノイズ耐性を確保できます。0.2 VのULVRモードでは、提案の8TUセルは従来の低電圧セルよりもはるかに強いノイズ耐性を示し、さらに0.16 Vでも安定なデータ保持が可能です。

最後に、提案した8TUセルでメモリアレイを構成した8 kB ULVR-SRAMマクロ[用語4]を開発しました。このSRAMマクロでULVRモードを用いた場合、従来セルを用いたSRAMマクロと比較して93%の待機時電力を削減できることを明らかにしました。これは不揮発性メモリの待機時電力削減能力に匹敵します。本成果は、IEEE(米国電気電子学会)の「IEEE Open Journal of Circuits and Systems」に9月3日付で掲載されました。

背景

CMOSトランジスタで構成されるメモリであるSRAMは、マイクロプロセッサやAIアクセラレータなどのCMOSロジックシステムに用いられる重要な記憶回路です。SRAMのリーク電力は、ロジックシステムの待機時電力だけでなく、AIアクセラレータのエネルギー効率も決める重要なファクターであることが分かっています。通常、SRAMは6つのトランジスタからなる記憶セル(6Tセル)を用いて構成されますが、このようなリーク電力の削減の要求に対応することは容易ではありません。

CMOSロジックシステムの待機時電力の削減方法として、システム内の部分的な電源遮断を用いたパワーゲーティング(PG)[用語5]がありますが、SRAMは揮発性メモリであるため、PGを実施することはできません。しかし、CMOSの動作電圧としては極めて低い、わずか0.2 V程度の超低電圧でデータを保持する超低電圧リテンション(ULVR)が可能であれば、SRAMでも実質的なPGを実現できます。これは完全な電源遮断ではありませんが、SRAMの待機時電力を90%以上削減できます。また、SRAMの低リークのULVRモードは、AIアクセラレータのエネルギー効率を最大化できる高性能化技術であるエネルギー最小点(EMP)[用語6]動作にも応用できます。本研究グループはこれまで、ULVRが可能なSRAM(ULVR-SRAM)の研究・開発を進めてきました。今回の研究では0.2 Vの超低電圧において低リークでありながら、さらにノイズ耐性を向上できる新たなULVR-SRAMを開発しました。

研究成果

新型インバータの開発

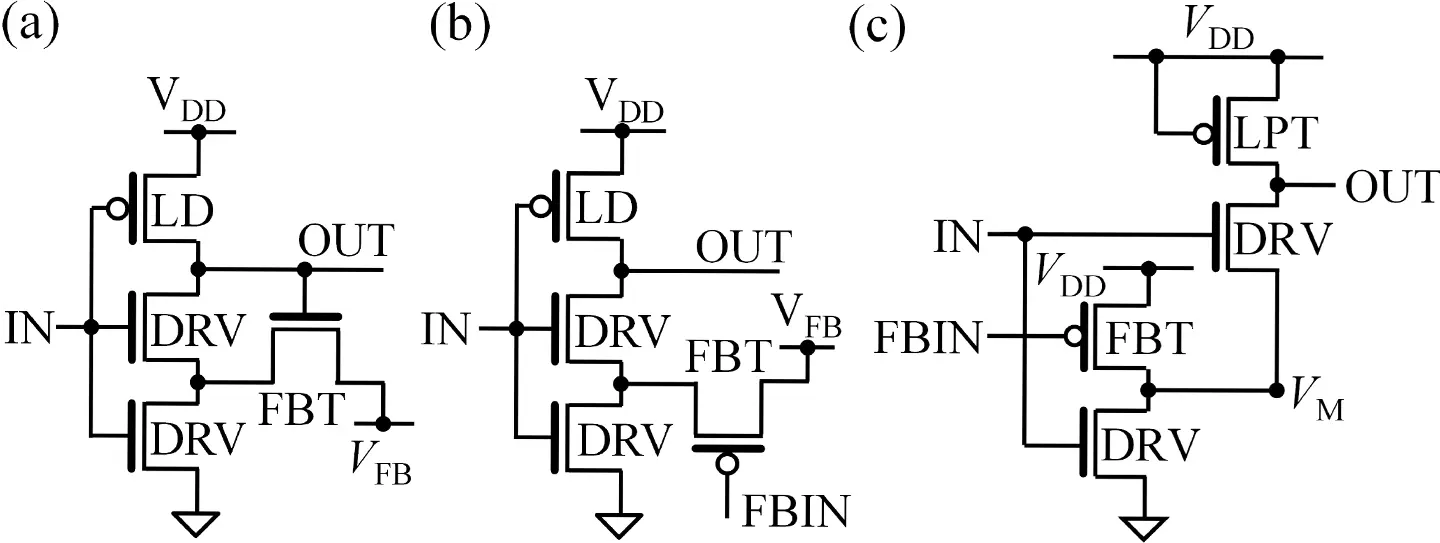

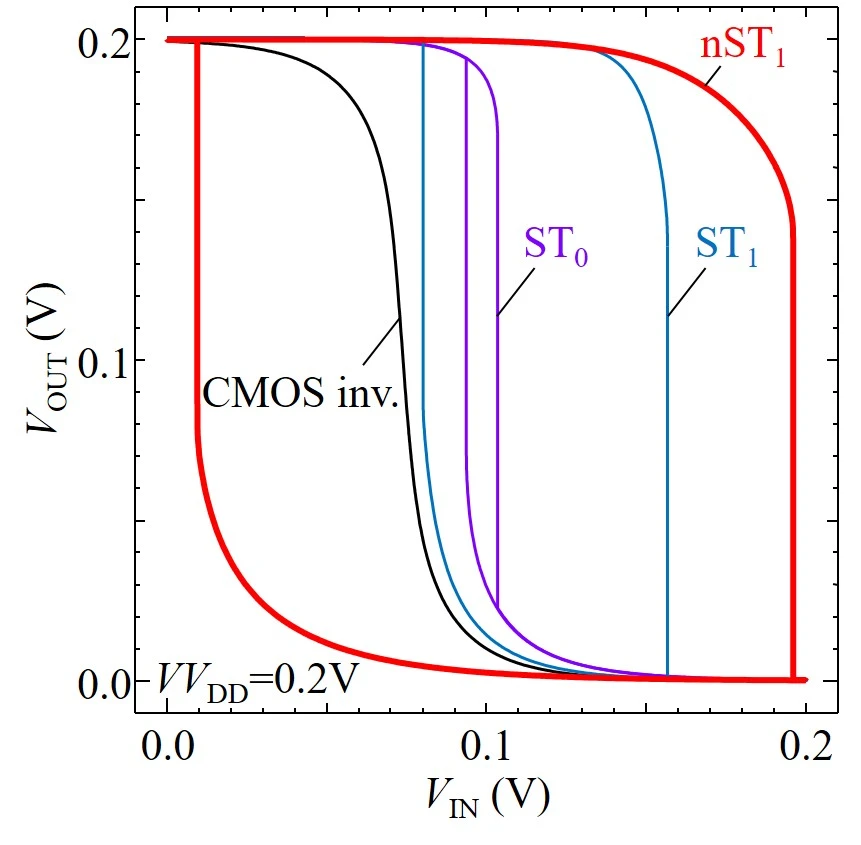

ULVR-SRAMの記憶セルを実現するためには、低電圧でもヒステリシスのある角形の伝達特性(VTC)を示すインバータを用いることが重要です。本研究ではまず、VTCのヒステリシス幅を最大化できる新しいインバータを開発しました。この技術の基礎となっているのは、シュミットトリガ型のインバータですが、図1(a)に示す従来型のシュミットトリガ(ST0)インバータの回路構成では、0.2 Vのような極めて低い電圧では十分なヒステリシス幅は得られません(図2)。そこで本研究グループでは、これまで、新たな構成のシュミットトリガ(ST1)インバータの開発を進めてきました。図1(b)に示すST1インバータを用いれば、ヒステリシス幅は大きく広がり(図2)、ULVR-SRAMの実現が可能になります。ULVR-SRAMの性能をさらに向上させ、より低い電圧でのULVRを実現するには、このヒステリシス幅を最大限までに広げることが重要になります。

本研究で提案したインバータ(nST1)の回路構成を図1(c)に示します。nST1インバータは、ST1インバータにおける入力段のpMOSを入力から切り離し、入力段インバータを擬似nMOS構成としたものに相当します。このpMOS(図1(c)中のLPT)は遮断(またはそれに近い状態)で用います。すなわち、nST1インバータはLPTによるリーク電流(またはそれに近い電流)で駆動されます。図2に示すように、nST1インバータの0.2 Vにおける電圧伝達特性(VTC)は、ヒステリシス幅がほぼ最大限に拡大できていることが確認できます。また、同図からST0,ST1インバータに比べて非常に大きなヒステリシス幅を実現できていることが分かります。

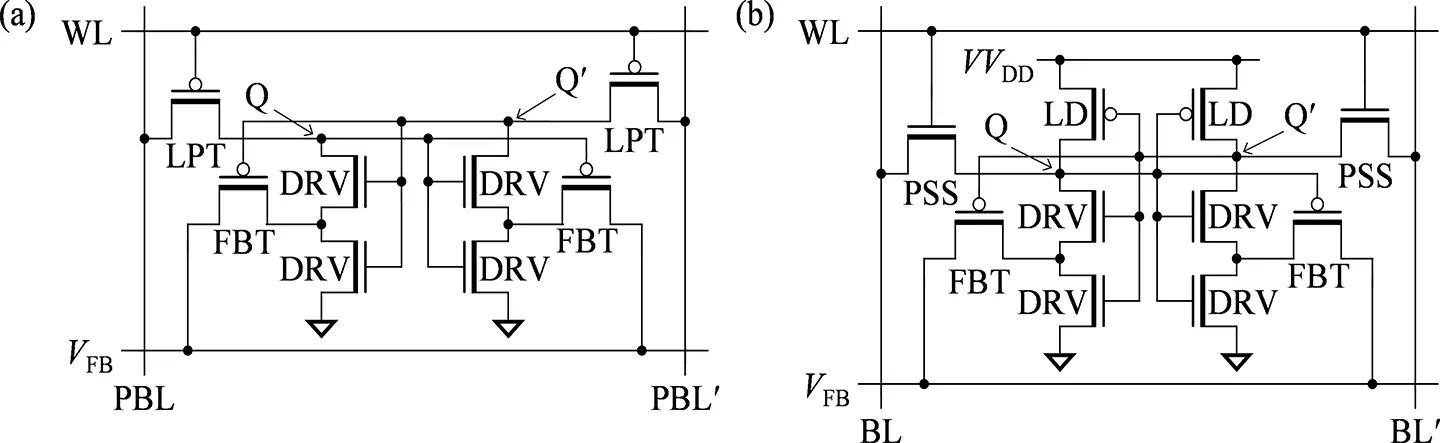

新型ULVR-SRAMセルの開発と不良率解析

次に、nST1インバータを用いて新型のULVR-SRAMセルを開発しました。図3(a)にnST1インバータで構成したセルを示します。このセルでは、従来のSRAMセルにおけるロードトランジスタ(LD)とパストランジスタ(PSS)を1つのトランジスタ(LPT)に統合できるため、少ないトランジスタ数でセルを構成できます。ST1インバータで構成したセル(10TU)が10トランジスタ構成であるのに対して (図3(b))、今回開発したセルは8トランジスタ構成になっています。この8TUセルでは、PBLとPBL´は、通常はセルの電源線として用いますが、読み出し時にはビット線として用いています。したがって、LPTは、通常はセルに電力供給するロードトランジスタとして機能しますが、読み出し時にはセル状態の記憶状態に対応して、PBLまたはPBL´のどちらかを放電するパストランジスタの機能を担います。この8TUセルに対して、擬スタティッノイズマージン(QSNM)と消費電力を設計指標として、セル構造の最適化を行いました。

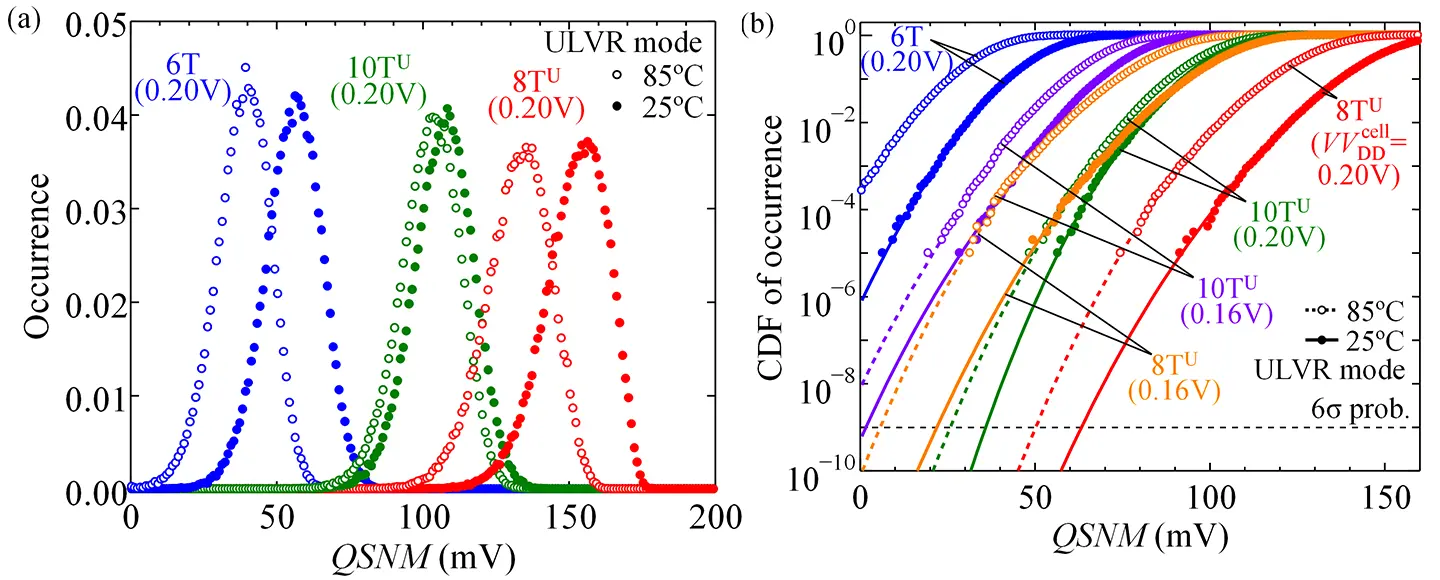

この最適化したセルについて、トランジスタのランダムなローカルばらつきを考慮したモンテカルロシミュレーションにより不良率解析を行いました。セルの不良率は各セルのULVRモードにおけるQSNMの分散の累積分布(CDF)から解析できます。動作電圧が0.2 V、動作温度が25ºCおよび85ºC の条件で、8TUセル(nST1インバータで構成)、10TUセル(ST1インバータで構成)、および、従来の6TセルのULVRモードにおけるQSNMの分散を比較したところ、 図4(a)に示すように8TUセルのQSNMの分布はどのセルより高い電圧側に位置し、最も強いノイズ耐性があることが分かりました。各セルのULVRモードにおけるQSNMのCDFを図4(b)に示します。6σ不良率(図中の破線)におけるQSNMの値が正であれば、原理的には6σ不良率を満足すると判定できます(ただし通常はある程度の基準を設ける)。動作電圧が0.2 Vのとき、8TUセルと10TUセルは、25℃と85℃でこの基準の6σ不良率を満たします。特に 8TUセルの6σ不良率におけるQSNMは、10TUセルの2倍程度の極めて高い値となります。一方、6TセルはULVRモードにおいて6σ不良率を満たすことはできません。さらに8TUセルは、動作電圧が0.16 Vであってもこの非常に低い不良率を満たすことができます。

新規セルを用いたULVR-SRAMマクロ

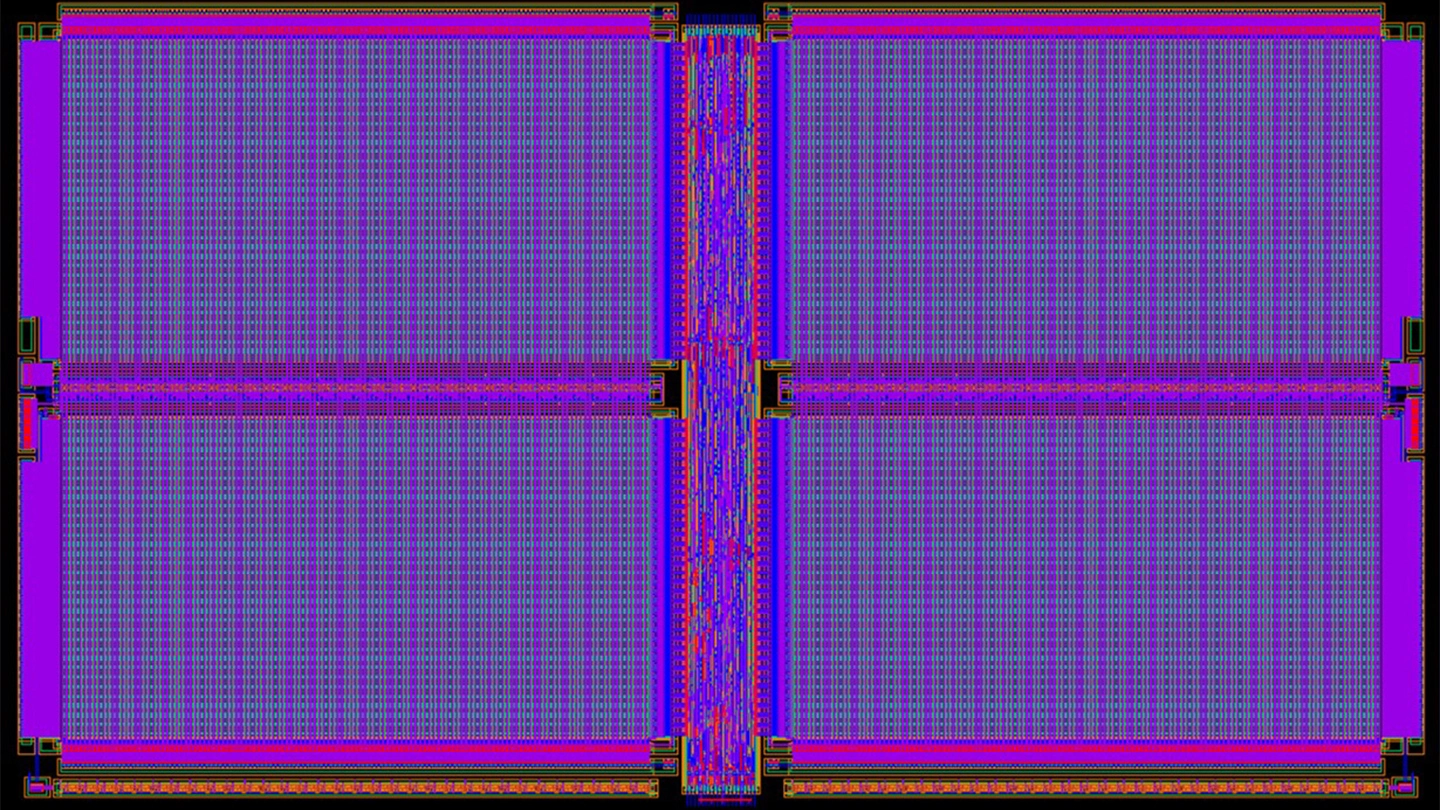

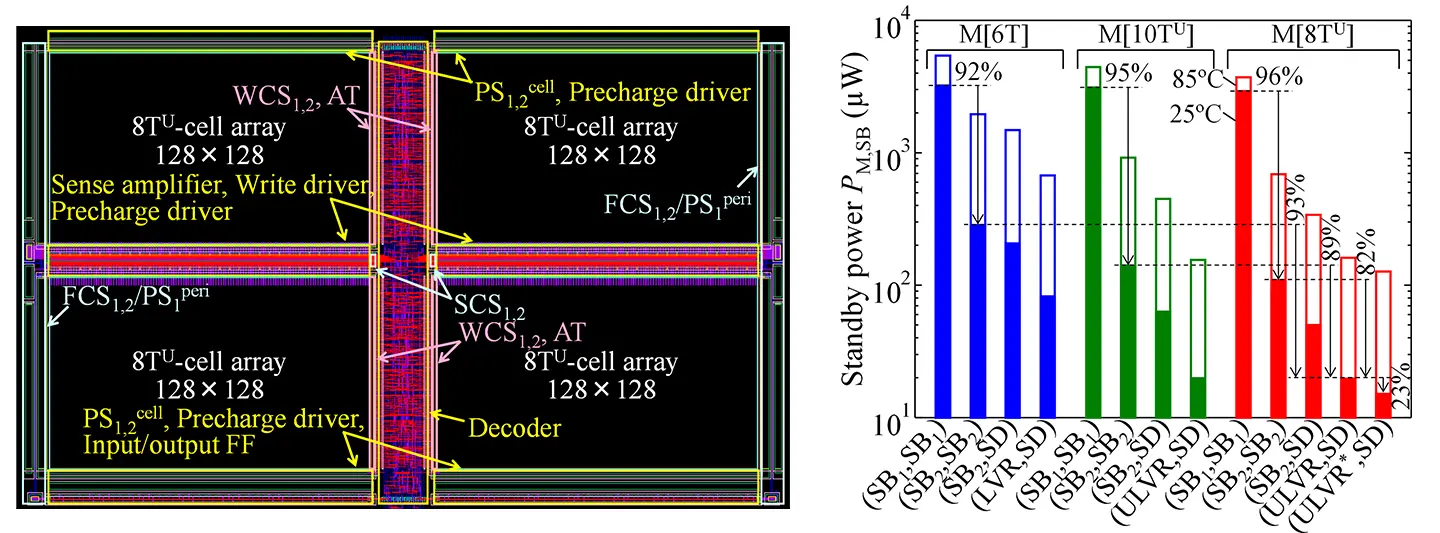

最適設計された8TUセルを用いて、8 kBのマクロ(M[8TU])を開発しました。設計したマクロのレイアウトを図5(a)に示します。また比較のために、6Tセルと10TUセルを用いたマクロ(M[6T]とM[10TU])も設計しました。これらのマクロの性能を高速SPICE (FineSim)による大規模シミュレーションを用いて解析しました。

図5(b)にM[8TU]、M[10TU]、M[6T]の待機時電力を示します。各マクロの待機時電力は(セルアレイ, 周辺回路)= (SB1, SB1), (SB2, SB2), (SB2, SD), (ULVR , SD)の条件で解析しました。SB1、SB2、ULVR、SDはそれぞれ、スタンバイ(クロック有)、スタンバイ(クロックゲーティング)、超低電圧リテンション、電源遮断の各モードを表します。

今回開発したM[8TU]はどの動作モードでも待機時電力が低く、特に(ULVR, SD)モードとすることで大幅に待機時電力を削減できます。これをM[6T] の(SB2, SB2)モードと比較すると、93%の削減になります。また、M[8TU]はより低い電圧でのデータ保持も可能であり、0.16 VのULVRモード(図5(b)中のULVR*)では待機時電力はさらに低くなり、0.2 V のULVR時から23%も削減できます。

社会的インパクト

本研究では、わずか0.2 V程度の超低電圧でSRAMセルのノイズマージンを最大限に拡大できる新たなCMOSインバータを提案し、このインバータを用いてULVR可能な新しいSRAMセルを開発しました。このSRAMのULVRモードを用いれば、実質的なPGによってデータを失うことなく、待機時電力を不揮発性メモリ並みに削減することが可能になります。

本技術は、待機時電力の削減が重要となるIoTデバイスやモバイルエッジ・デバイスに搭載されるCMOSロジックシステムへの応用が期待されます。特に、このような応用で重要となるシステムの低電圧動作では、全電力に対する待機時電力の割合が大きくなることから、実質的なPGによって待機時電力を削減できる本技術は有効になると考えられます。これにより微弱な環境発電下や長期のバッテリー利用を前提とする新たな応用へとCMOSロジックシステムの利用を拡大できます。

今後の展開

SRAMのリーク電力の削減はロジックシステムの待機時電力の削減だけでなく、AIアクセラレータのエネルギー効率を決める重要なファクターにもなります。近年注目を集めているProcessing-in-Memory (PIM)型のアクセラレータでは、積和演算の並列化とともにエネルギー最小点(EMP)が減少し、それにともなってエネルギー効率の最大値も増大します。このようなPIMでは、0.3 V以下のEMPにも対応する必要があります。本研究で開発したSRAMのULVRモードは、セルに工夫を加えることでデータ保持だけでなく、このような低電圧のEMP下でのSRAM動作も可能にします。したがって、本技術はPIM型AIアクセラレータの高性能化にも展開できます。

参考文献

- [1]

- Yoshida, Y. Shiotsu, D. Kitagata, S. Yamamoto,and S. Sugahara,IEEE Open J. Circuits Syst., vol. 2, pp. 520–533, 2021

- [2]

- Shiotsu and S. Sugahara, IEEE J. Explor. Solid-State Comput. Devices Circuits, vol. 8, pp. 134–144, 2022.

- [3]

- Shiotsu and S. Sugahara, IEEE J. Explor. Solid-State Comput. Devices Circuits,vol. 11, pp. 25–33, 2025.

用語説明

- [用語1]

- アクセラレータ:特定の処理を高速化できるハードウェアまたは演算システム。特に、AIシステムでは、各種ニューラルネットワーク(NN)による推論処理に特化した専用のアクセラレータが用いられることが多い。AI分野では、NNアクセラレータやAIアクセラレータとも呼ばれる。

- [用語2]

- 超低電圧リテンション(ULVR):2 V程度以下というCMOSの動作電圧としては非常に低い電圧で、高い信頼性(極めて低い不良率)を確保しデータを保持する動作モード。ULVRでは超低電圧でデータを保持のみを行い、読み出しや書き込みといった動作は行わないが、実質的なパワーゲーティングに応用できる。

- [用語3]

- 擬似nMOSインバータ:通常のCMOSインバータのpMOSの入力を切り離し、このpMOSを適宜バイアスして負荷抵抗に用いるインバータ構成。通常、このpMOSは導通状態で用いるが、本研究で開発したインバータでは、遮断状態で生じるリーク電流を用いているため、セルリークを低く抑えることができる。また、切り離されたpMOSは、回路上の工夫によってSRAMセルのトランジスタ数の削減にも有効になる。

- [用語4]

- マクロ:特定の機能を持つ回路ブロック。例えば、SRAMでは比較的小さな記憶容量( 数kB程度)のマクロを作っておき、これを複数個組み合わせることで所望のサイズのメモリを実現する。

- [用語5]

- パワーゲーティング(PG):システムを適宜ブロックに分割し、そのブロックが待機時状態にある場合には、そのブロックの電源を遮断して待機時電力を削減する技術。このブロックはパワードメインと呼ばれ、パワードメインの電源遮断にはパワースイッチと呼ばれるトランジスタが用いられる。

- [用語6]

- エネルギー最小点(EMP):CMOSロジックシステムで消費される全エネルギーは回路動作に基づく動作時エネルギーと、トランジスタのリーク電流によって生じる待機時エネルギーからなる。これらはそれぞれ異なる電圧依存性を有することから、全エネルギーは特定の電圧で最小値をとる。この全エネルギーが最小となる動作点がEMPである。EMPを動作電圧とすることで、エネルギー効率を最大化できる。

論文情報

- 掲載誌:

- IEEE Open Journal of Circuits and Systems

- タイトル:

- A New Ultralow-Voltage Retention SRAM Cell Enhancing Noise Immunity

- 著者:

- Katsutoshi Ito, Yusaku Shiotsu, and Satoshi Sugahara

研究者プロフィール

菅原 聡 Satoshi Sugahara

東京科学大学 総合研究院 未来産業技術研究所 准教授

研究分野:集積回路、集積デバイス

塩津 勇作 Yusaku Shiotsu

東京科学大学 総合研究院 未来産業技術研究所 研究員

研究分野:集積回路

伊藤 克俊 Katsutoshi Ito

東京科学大学 工学院 電気電子系 大学院生(修士課程2年、研究当時)

研究分野:集積回路

関連リンク

東京科学大学 総合研究院 未来産業技術研究所

博士研究員 塩津 勇作

- Tel

- 045-924-5456

- Fax

- 045-924-5456