どんな研究?

動画を見たり、AIに質問したりするとき、コンピュータの中では膨大なデータが動いています。特にAIの計算を支えるデータセンターでは、膨大なデータを高速でやり取りする必要があります。しかし現在のコンピュータには、大きな弱点があります。それは「計算する場所」と「データを保存する場所」が離れていることです。

そのため、データはチップの中を何度も往復しなければなりません。このデータの行き来に時間がかかることが原因となり、速度や消費電力の限界につながっています。

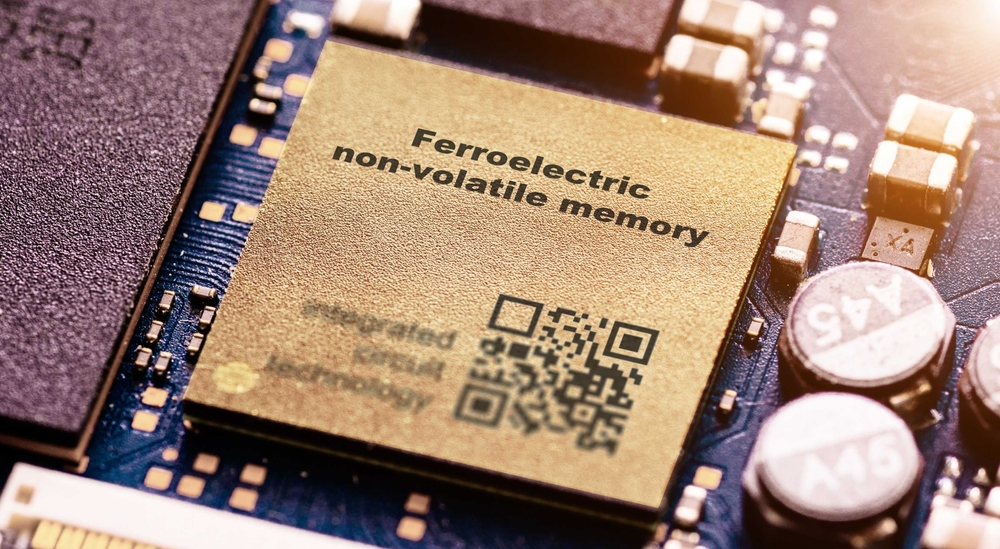

この問題を解決する方法の一つが、計算する回路のすぐ近くにメモリを置くことです。そうすれば、データがチップの中を行き来する距離を減らすことができます。このように、計算回路とメモリを一体化させる仕組みは「ロジック混載メモリ」と呼ばれ、世界中で研究が進められています。その材料として注目されているのが、窒化アルミニウムスカンジウムという物質です。この材料は、電源を切っても情報を保持できる性質を持ち、しかも高温の製造工程にも強いことが知られていました。

これまでの研究では主に窒化アルミニウムスカンジウムという材料を薄い層として作り、その厚さをどこまで小さくできるかが調べられてきました。しかし実際のメモリ装置は、電極などいくつもの層が重なった構造になっています。そのため、装置全体をどこまで小さくできるのかは、まだよく分かっていませんでした。

そこで東京科学大学(Science Tokyo)の舟窪浩(ふなくぼ・ひろし)教授らの研究チームは、メモリ素子全体を極限まで薄くすることに挑みました。

ここが重要

研究チームは、白金の電極と窒化アルミニウムスカンジウムの薄い膜を組み合わせ、メモリ素子の厚さをわずか30ナノメートルまで小さくすることに成功しました。これは髪の毛の太さの3,000分の1ほどしかありません。

難しかったのは、ただ薄くするだけでは性能が保てないことでした。膜を薄くすると、内部の結晶の並び方が乱れ、メモリとしての働きが弱くなってしまうことがあったのです。そこで研究チームは、膜の下にある電極をあらかじめ熱で処理する方法を試しました。すると、その上に作られる膜の結晶がきれいにそろい、20ナノメートルという薄さでも高い性能を維持できることが分かりました。さらに電極そのものを5ナノメートルまで薄くしても問題がないことが確認され、メモリ素子全体を小さくする新しい設計の可能性が示されました。

今後の展望

今回の成果は、計算回路とメモリを一体化した新しい半導体チップの実現につながると期待されています。もしこうしたメモリが実用化されれば、データの往復が減るため、コンピュータはより速く、しかも少ない電力で動くようになります。これはAIを支えるデータセンターや、身の回りのIoT機器など、さまざまな分野で役立つ可能性があります。

また、現在の半導体製造技術とも組み合わせやすいため、将来の高性能チップに組み込まれることも期待されています。

研究者のひとこと

素子全体をどこまで薄くできるのかは、これまでほとんど分かっていませんでした。電極の処理方法など細かな条件を一つ一つ試しながら、ようやく30ナノメートルという厚さでも性能を保てることを示すことができました。エネルギー消費を劇的に抑えた将来のコンピュータの技術につながることを期待しています。

(舟窪浩:東京科学大学 物質理工学院 材料系 教授)

この研究をもっと詳しく知るには

お問い合わせ

研究支援窓口