ポイント

- スカンジウム置換アルミニウム窒化物薄膜を用いた強誘電体キャパシタで、総膜厚30 nmまでの大幅なスケールダウンに成功。

- ロジック混載メモリなどの半導体デバイスへの実装が可能なレベルの薄膜化を実現。

- 高い強誘電性を生かした高集積強誘電体メモリ実用化の加速に期待。

概要

東京科学大学(Science Tokyo)物質理工学院 材料系の道古宗俊大学院生(兼 キヤノンアネルバ株式会社)、岡本一輝助教、舟窪浩教授、およびキヤノンアネルバ株式会社の松井尚子氏、入澤寿和氏、恒川孝二氏らの研究グループは、窒化物強誘電体であるスカンジウム置換アルミニウム窒化物((Al,Sc)N)の薄膜を用いて、電極-強誘電体-電極の3層からなる強誘電体キャパシタ構造を、総膜厚30 nmまで薄膜化することに成功しました。

強誘電体メモリは、データストレージとロジック機能を同一デバイス内に統合できるロジック混載メモリ[用語1]に適した、次世代型の不揮発性メモリとして注目を集めています。ただし、ロジック混載メモリに統合するには、強誘電体キャパシタ構造の膜厚を金属配線層間以下にする必要があるため、メモリデバイスの薄型化が重要になります。しかしこれまでは、電極も含めた(Al,Sc)Nキャパシタの総膜厚に関する研究はほとんど行われていませんでした。

本研究では、(Al,Sc)N膜とPt電極を用いた強誘電体キャパシタにおいて、積層構造の総膜厚を30 nmまで薄くすることに初めて成功しました。この成果により、(Al,Sc)N膜を用いた強誘電体メモリ[用語2]を、ロジック混載メモリに適用可能な薄い総膜厚で作製できるようになりました。この薄膜化技術を応用することで、メモリ容量を支配する高い強誘電性(残留分極値[用語3])を持つ(Al,Sc)N膜のデバイスの実用化が期待できます。

本成果は、11月7日付(現地時間)で「Advanced Electronic Materials」誌に掲載されました。

背景

現在、データストレージとロジック機能を同一デバイス内に統合できる、ロジック混載メモリが注目を集めています[参考文献1]。ロジック混載メモリをデバイスに適用すると、別個のメモリユニットと処理ユニット間のデータ転送を削減でき、半導体デバイスの高性能化や劇的な低消費電力化につながります。こうしたメモリ技術は、データサーバーやInternet of Things(IoT)デバイス向けに高い需要があります[参考文献2-3]。

このロジック混載メモリに適した次世代型の不揮発性メモリの1つとして、強誘電体メモリの開発が活発に行われています[参考文献4]。強誘電体メモリは、集積回路の金属配線層間に挿入することで、ロジック混載メモリへ統合できると期待されています。ただしこの場合、電極-強誘電体-電極の3層からなる強誘電体キャパシタ構造の総膜厚の薄膜化(膜厚のスケーリング)が重要な課題となります。そのためには、電極を含む強誘電体キャパシタの各層の膜厚を最小限に抑えることが求められます。

ウルツ鉱構造[用語4]を有するスカンジウム置換アルミニウム窒化物((Al,Sc)N)は、従来の強誘電体材料よりも高い強誘電性(残留分極値)を示すため、キャパシタ構造の3次元化が難しいロジック混載メモリに適した材料として注目を集めています。強誘電体の (Al,Sc)N膜の薄膜化(膜厚のスケーリング)についてはすでに研究が行われていますが、ロジック混載メモリで用いることを目指した、メモリデバイス全体の膜厚に関する研究はほとんど行われていません。そのため、電極材料や(Al,Sc)N膜を薄膜化した場合の膜特性への影響は、これまで十分に解明されていませんでした。

研究成果

本研究では、ロジック混載メモリに応用可能な(Al,Sc)N膜の特性を調べ、メモリデバイス総膜厚のスケーリングを行いました。

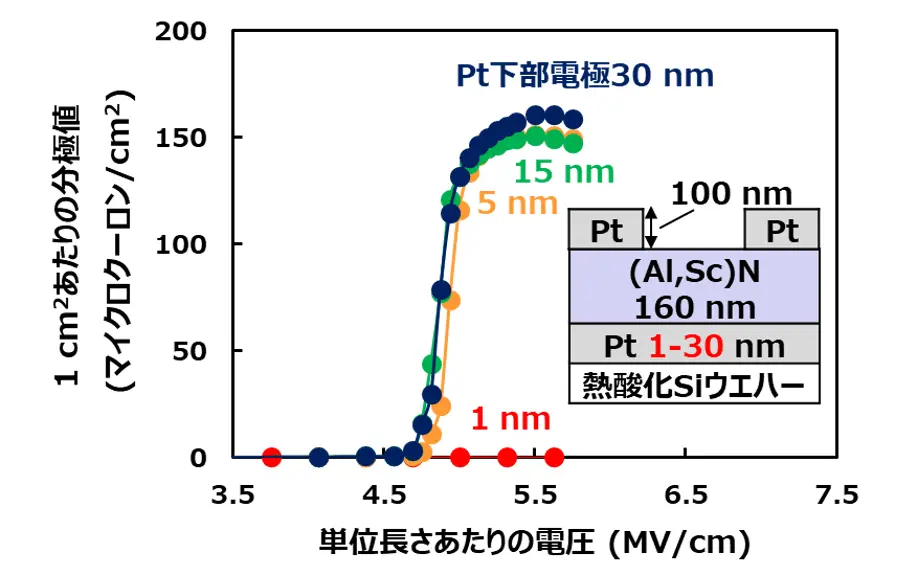

最初に、Pt下部電極をさまざまな膜厚で成膜し、その上に成膜した(Al,Sc)N膜の強誘電特性[用語5]を評価しました。その結果、下部電極の膜厚を5 nmまで薄膜化しても、(Al,Sc)N膜の強誘電性が劣化しないことが分かりました(図1)。

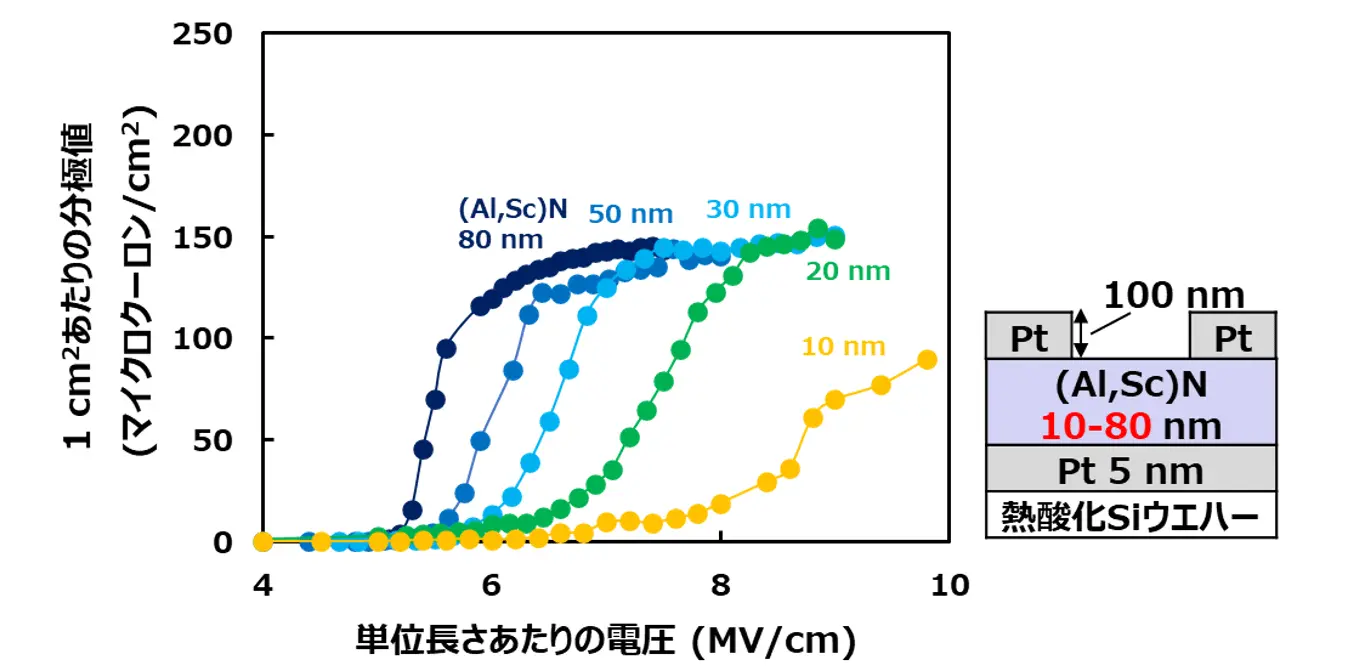

次に、5 nmまで薄膜化したPt下部電極上に、さまざまな膜厚の(Al,Sc)N膜を成膜し、強誘電特性の評価を行いました。その結果、膜厚5 nm のPt下部電極上に成膜した(Al,Sc)N膜は、膜厚20 nmまで薄膜化しても強誘電性が劣化せず、さらに膜厚10 nmでも高い強誘電性が得られることが明らかになりました(図2)。

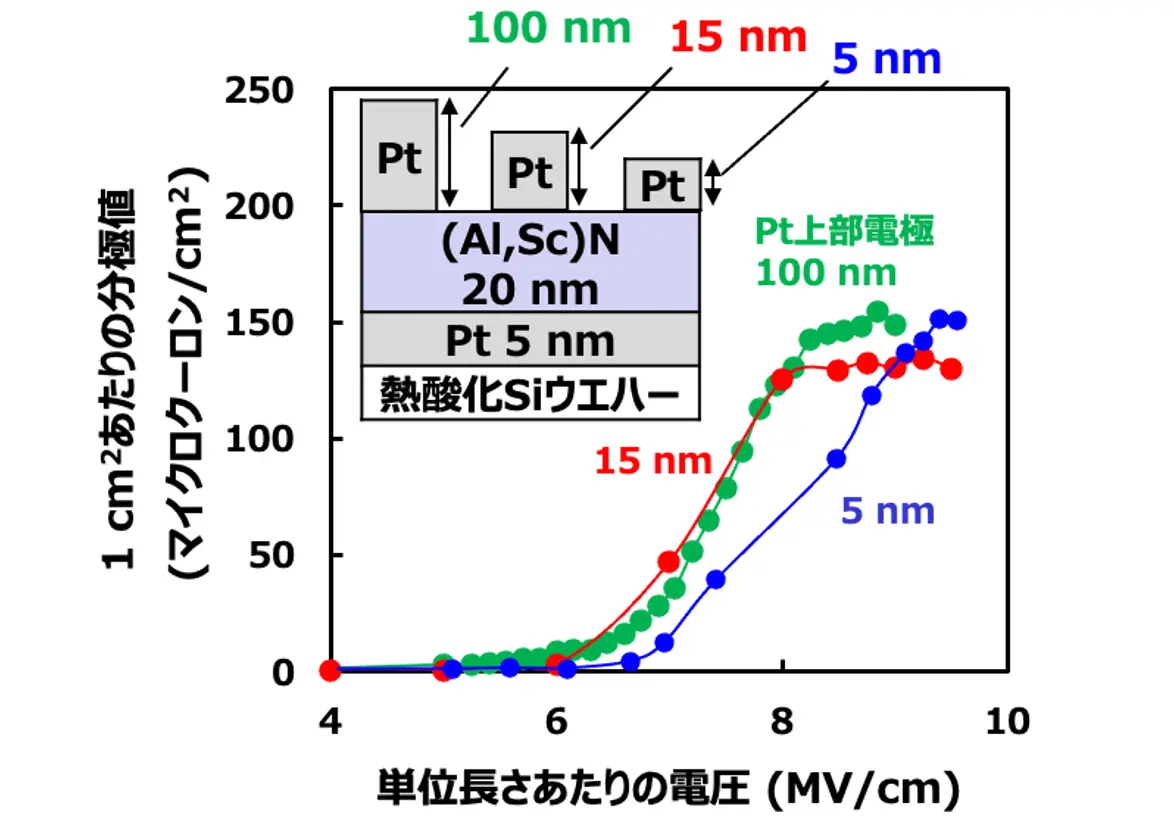

最後に、5 nmに薄膜化したPt下部電極と、20 nmに薄膜化した (Al,Sc)N膜の上に、さまざまな膜厚のPt上部電極を成膜し、(Al,Sc)N膜の強誘電特性を評価しました。その結果、Pt上部電極の膜厚を5 nmまで薄膜化しても、(Al,Sc)N膜の強誘電性はほとんど劣化しないことが明らかになりました(図3)。最終的には、各部の膜厚をPt下部電極で5 nm、(Al,Sc)N膜で20 nm、Pt上部電極で5 nmまで薄くし、総膜厚を30 nmまで薄膜化することに成功しました。

社会的インパクト

今回の研究で、スカンジウム置換アルミニウム窒化物((Al,Sc)N)では、強誘電体キャパシタの総膜厚を30 nmまで薄膜化できることが明らかになりました。この成果には、次のような波及効果が考えられます。

a)新規窒化物を用いた強誘電体メモリのロジック混載メモリ化の加速

今回、メモリデバイスの総膜厚の薄膜化に成功したことで、実用化に向けての課題だった、集積回路の金属配線層間への挿入が実現可能になりました。これにより、メモリ能力(残留分極値)が大きい新規窒化物を用いた強誘電体メモリを、ロジック混載の高集積化メモリに適用できるようになります。

b)新規強誘電体メモリの実用化の加速

(Al,Sc)N膜は、膜厚5 nm以下に薄膜化しても強誘電性が劣化しないことがすでに確認されているため、その大きな強誘電性を生かした、強誘電体のトンネル電流を用いる新たな強誘電体メモリ(強誘電体トンネルジャンクション)を実現できます。今回の研究では、下部電極の結晶性改善によって、(Al,Sc)N膜の薄膜化が可能であることが明らかになりました。今後、電極も含めたキャパシタ構造全体の材料プロセスの検討により、 (Al,Sc)N膜のさらなる薄膜化が期待できます。

c)高性能圧電デバイス応用拡大の加速

(Al,Sc)N膜は圧電デバイス[用語6]向けの材料としても注目されており、5G通信向けの高周波フィルタや高感度MEMSセンサーなどへの応用が見込まれます。本研究で確立した、(Al,Sc)N薄膜成長技術や、強誘電体と電極界面の制御技術は、こうした圧電デバイスでも高い結晶性と安定した機械的応答を実現する鍵となります。今回の成果は今後、高い圧電性を持つ (Al,Sc)N材料の特性を生かした、圧電デバイスのプロセス最適化の指針となることが期待できます。

今後の展開

本研究によって、(Al,Sc)Nキャパシタ構造がロジック混載メモリに適用可能なレベルに薄い総膜厚で作製可能であり、メモリ容量を支配する高い強誘電性 (残留分極値) を持つ (Al,Sc)N膜のデバイスへの実用化が期待できることを解明しました。今後は、よりメモリプロセスに適した電極材料の検討、メモリ動作電圧の低減に向けた開発を行い、実デバイスへ実装可能なプロセス最適化の研究を行っていきます。

付記

今回の研究の一部は、国立研究開発法人新エネルギー・産業技術総合開発機構(NEDO) (JPNP21009)、文部科学省の次世代X-nics半導体創生拠点形成事業(JPJ011438)、データ創出・活用型マテリアル研究開発プロジェクト事業(JPMXP1122683430)、および科学技術振興機構(JST)先端国際共同研究推進事業(ASPIRE)(JPMJAP2312)の助成を受けました。

参考文献

- [参考文献1]

- W. Haensch et al.:Adv. Mater. 2023, 35, 2204944.

- [参考文献2]

- C. Matsui et al.:Jpn. J. Appl. Phys. 2021, 60, SBBB05.

- [参考文献3]

- J. S. Yuan et al.:Electronics 2017, 6, 67.

- [参考文献4]

- A. Chavan et al.:IEEE IMW 2024.

用語説明

- [用語1]

- ロジック混載メモリ:プロセッサや制御回路などのロジック回路と同一チップ上にメモリ素子を集積した構造。

- [用語2]

- 強誘電体メモリ:強誘電体材料を用いた不揮発性メモリの総称。強誘電体材料を電極で挟んだ構造の強誘電体ランダムアクセスメモリ (FeRAM)、ゲート絶縁膜に強誘電体を用いたトランジスタの強誘電体ゲートトランジスタ (FeFET)、強誘電体薄膜をトンネル障壁として用い、分極方向に応じてトンネル電流が変化する現象を利用した強誘電体トンネルジャンクション (FTJ) の3つの方式が検討されている。

- [用語3]

- 残留分極値:強誘電体材料は、電界印加によって内部の電気双極子が整列し、電気分極が生じる。この際、電界印加をやめた後も、材料内部に分極が残る性質がある。この残った分極の大きさを残留分極値と呼ぶ。

- [用語4]

- ウルツ鉱構造:酸化亜鉛 (ZnO)、窒化アルミニウム (AlN) などで見られる、六方晶系に属する結晶構造の一種。原子は六方最密充填に近い配置をとり、各原子は4つの隣接原子と共有結合することで、四面体配位を形成する。

- [用語5]

- 強誘電特性:単位長さあたりに加えた電圧に対する電圧を除荷した際に残る1 cm2当たりの分極の値 (残留分極値) の変化。

- [用語6]

- 圧電デバイス:物質に圧力を加えると電気が発生し、逆に電気を加えると変形する「圧電効果」の性質を持つ圧電体材料を利用したデバイス。高周波信号を選択・制御するフィルタやMEMSセンサー向けデバイスとして用いられる。

論文情報

- 掲載誌:

- Advanced Electronic Materials

- タイトル:

- Thickness Scaling of Integrated Pt/(Al0.9Sc0.1)N/Pt Capacitor Stacks to 30 nm

- 著者:

- Soshun Doko, Naoko Matsui, Toshikazu Irisawa, Koji Tsunekawa, Nana Sun, Yoshiko Nakamura, Kazuki Okamoto, and Hiroshi Funakubo

研究者プロフィール

道古 宗俊 Soshun Doko

東京科学大学 物質理工学院 材料系

キヤノンアネルバ株式会社 装置事業部 プロセス開発部 プロセス開発第一課

研究分野:次世代型不揮発性メモリ向け薄膜の作製・特性評価

岡本 一輝 Kazuki Okamoto

東京科学大学 物質理工学院 材料系 助教

研究分野:強誘電体薄膜の作製・特性評価

舟窪 浩 Hiroshi Funakubo

東京科学大学 物質理工学院 材料系 教授

研究分野:新規誘電体、圧電体、強誘電体の開発、誘電体薄膜や機能性薄膜の合成

関連リンク

東京科学大学 物質理工学院 材料系/キヤノンアネルバ株式会社 装置事業部 プロセス開発部 プロセス開発第一課

道古 宗俊

- doko.soshun@mail.canon